# STATIC ANALYSIS FOR GPU PROGRAM PERFORMANCE

# Nimit Singhania

#### A DISSERTATION

Computer and Information Science

Presented to the Faculties of the University of Pennsylvania Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

2018

Supervisor of Dissertation Co-Supervisor of Dissertation

Rajeev Alur Joseph Devietti

Zisman Family Professor of

Assistant Professor of Computer and

Computer and Information Science Information Science

Graduate Group Chairperson

Rajeev Alur Zisman Family Professor of Computer and Information Science

## **Dissertation Committee**

Stephan Zdancewic, Professor of Computer and Information Science Mayur Naik, Associate Professor of Computer and Information Science Sampath Kannan, Henry Salvatori Professor of Computer and Information Science Vinod Grover, Director of Engineering, NVIDIA

## **ABSTRACT**

## STATIC ANALYSIS FOR GPU PROGRAM PERFORMANCE

## Nimit Singhania

# Rajeev Alur Joseph Devietti

GPUs have become popular due to their high computational power. Data scientists rely on GPUs to process loads of data being generated by their systems. From a humble beginning as a graphics accelerator for arcade games, they have become essential compute units in many important applications. The programming infrastructure for GPU programs is still rudimentary and the GPU programmer needs to understand the intricacies of GPU architecture, tune various execution parameters and optimize parts of the program using low-level primitives. GPU compilers are still far from the automation provided by CPU compilers where the programmer is often oblivious of the details of the underlying architecture.

In this work, we present *light-weight formal* approaches to improve performance of *general* GPU programs. This enables our tools to be fast, correct and accessible to everyone. We present three works. First, we present a compile-time analysis to identify uncoalesced accesses in GPU programs. Uncoalesced accesses are a well-documented memory access pattern that leads to poor performance. Second, we present an analysis to verify block-size independence of GPU programs. Block-size is an execution parameter that must be tuned to optimally utilize GPU resources. We present a static analysis to verify block-size independence for *synchronization-free* GPU programs and ensure that modifying block-size does not break program functionality. Finally, we present a compile-time optimization to leverage cache reuse in GPU to improve performance of GPU programs. GPUs often abandon cache reuse-based performance improvement in favor of thread-level parallelism, where a large number of threads are executed to hide latency of memory and compute operations.

We define a compile-time analysis to identify programs with significant intra-thread locality and little inter-thread locality, where cache resue is useful, and a transformation to modify block-size which indirectly influences the hardware thread-scheduler to improve cache utilization.

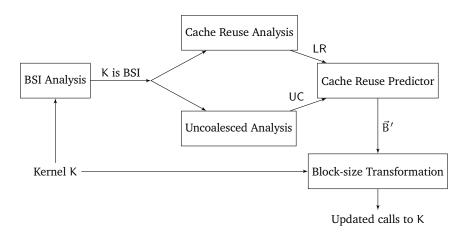

We have implemented the above approaches in LLVM and evaluate them on various benchmarks. The uncoalesced access analysis identifies 111 accesses, the block-size independence analysis verifies 35 block-size independent kernels and the cache reuse optimization improves performance by an average  $1.3\times$  on two Nvidia GPUs. The approaches are fast and finish within few seconds for most programs.

This thesis is based on material drawn from the following publications:

- Rajeev Alur, Joseph Devietti, Omar S. Navarro Leija and Nimit Singhania. GPUDrano: Detecting Uncoalesced Accesses in GPU Programs. In *Proceedings of the 29th International Conference on Computer-Aided Verification*, CAV 2017, pages 507-525. Springer, 2017.

- 2. Rajeev Alur, Joseph Devietti and Nimit Singhania. Block-Size Independence for GPU Programs. In *Proceedings of the 25th International Symposium on Static Analysis*, SAS 2018, pages 107-126. Springer, 2018.

- 3. Rajeev Alur, Joseph Devietti and Nimit Singhania. Static Analysis for Cache Reuse Optimization in GPU Programs. In submission, 2018.

# **Contents**

| 1 | A Formal Perspective to GPU Computing           | 1  |

|---|-------------------------------------------------|----|

|   | 1.1 Challenges with GPU Programming             | 3  |

|   | 1.2 Structured Parallelism                      | 4  |

|   | 1.3 Organization                                | 6  |

| 2 | Fundamentals of GPU Programming                 | 7  |

|   | 2.1 Background                                  | 7  |

|   | 2.1.1 GPU Programming Model                     | 8  |

|   | 2.1.2 GPU Architecture                          | 11 |

|   | 2.2 Example: Gaussian Elimination               | 12 |

|   | 2.3 Formal Model                                | 14 |

|   | 2.3.1 Programming Model                         | 15 |

|   | 2.3.2 Execution Model                           | 17 |

|   | 2.3.3 Memory Performance Model                  | 20 |

|   | 2.4 Limitations of Formalization                | 22 |

|   | 2.5 Conclusion                                  | 24 |

| 3 | Abstract Execution-based Static Analyses        | 25 |

|   | 3.1 Abstract Domain                             | 26 |

|   | 3.1.1 Example: Divide-by-zero Error             | 26 |

|   | 3.1.2 Abstract Values and Abstract State        | 27 |

|   | 3.2 Abstract Semantics                          | 28 |

|   | 3.3 Abstract Execution Engine                   | 30 |

|   | 3.4 Implementation                              | 33 |

|   | 3.5 Other Approaches                            | 34 |

|   | 3.6 Conclusion                                  | 34 |

| 4 | Static Detection of Uncoalesced Accesses        | 35 |

|   | 4.1 An Uncoalesced Access: Gaussian Elimination | 37 |

|   | 4.2 Formalization                               | 38 |

|   | 4.3 Detecting Uncoalesced Accesses              | 40 |

|   | 4.3.1 Abstract Domain                           | 40 |

|   | 4.3.2 Abstract Semantics                        | 43 |

|   | 4.3.3 Overall Analysis                          | 47 |

CONTENTS

| 7 | COH | cidding recinaries                                                              | / _             |

|---|-----|---------------------------------------------------------------------------------|-----------------|

| _ | Con | cluding Remarks                                                                 | 92              |

|   | 6.6 | Conclusion                                                                      | 91              |

|   |     | Related Work                                                                    | 88              |

|   |     | Evaluation                                                                      | 85              |

|   |     | 6.3.2 Block Size Transformation for Cache Reuse Optimization                    | 84              |

|   |     | 6.3.1 Cache Reuse Predictor for GPU Kernels                                     | 82              |

|   | 6.3 | Overall Approach                                                                | 81              |

|   |     | 6.2.3 Derived Increment Analysis                                                | 79              |

|   |     | 6.2.2 Simple Increment Analysis                                                 | 77              |

|   | 0.2 | 6.2.1 Loop Reusable Accesses                                                    | 75              |

|   |     | Cache Reuse Analysis                                                            | 73<br>74        |

| 6 |     | ic Analysis for Improving Cache Reuse  Example: Revisiting Gaussian Elimination | <b>71</b><br>73 |

|   | 5.5 | Conclusion                                                                      | 70              |

|   |     | Related Work                                                                    | 69              |

|   |     | Evaluation                                                                      | 68              |

|   | 5.2 | Analysis for Synchronization-free GPU Programs                                  | 63              |

|   |     | 5.1.2 Reduction to Thread-local Block Size Independence                         | 60              |

|   | J.1 | 5.1.1 Block Size Independence                                                   | 59              |

| 5 |     | ck-Size Independence for GPU Programs  Formalization                            | <b>57</b><br>59 |

|   |     |                                                                                 |                 |

|   |     | Related Work                                                                    | 55<br>56        |

|   |     | Evaluation                                                                      | 52              |

|   |     | 4.4.3 Handling Control Flow Graph Representation                                | 51              |

|   |     | 4.4.2 Handling Multiple Procedures                                              | 50              |

|   |     | 4.4.1 Handling Pointers and Structures                                          | 49              |

|   | 4.4 | Implementation                                                                  | 49              |

|   |     |                                                                                 |                 |

# **List of Tables**

| 4.1 | Evaluation results for static analysis to detect uncoalesced accesses. | <br> | 53 |

|-----|------------------------------------------------------------------------|------|----|

| 5.1 | Results of BSI analysis for Nvidia CUDA SDK 8.0 samples                | <br> | 68 |

# **List of Figures**

| 2.1 | Example 2-dimensional thread-grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Example GPU program: Gaussian elimination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9  |

| 2.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 |

| 2.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37 |

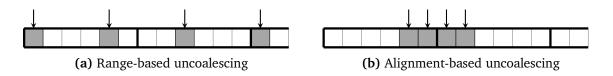

| 4.2 | Range-based and alignment-based uncoalesced accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39 |

|     | O Company of the comp | 44 |

| 4.4 | Abstract semantics for remaining statements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51 |

| 5.4 | Abstract semantics for block-size independence analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 |

| 5.5 | Analysis for first grid-dimension on the program in Figure 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57 |

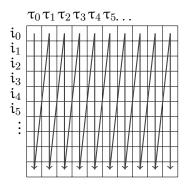

|     | 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73 |

| 6.2 | Abstract semantics for simple increment analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 78 |

|     | J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37 |

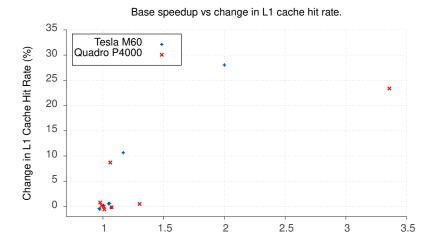

| 6.6 | Speedup against change in L1 cache hit rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

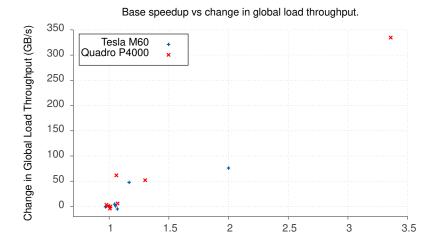

| 6.7 | Speedup against change in global throughput                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39 |

# List of Algorithms

| 3.1 Ab | stract Execution Engine | 31 |

|--------|-------------------------|----|

|--------|-------------------------|----|

# Chapter 1

# A Formal Perspective to GPU Computing

Graphics Processing Units, or GPUs, have emerged as a highly-parallel compute platform. Today, they are being used to accelerate numerous data-intensive applications. They have enabled large-scale machine learning and with that the resurgence of Artificial Intelligence. They are powering almost every critical scientific application, and the fastest supercomputers rely on GPUs to accelerate their computation. They have evolved into important compute units sharing the center stage with the CPU (Central Processing Unit).

This evolution has occurred over the course of time. The first GPUs were a set of specialized circuits used to accelerate graphics for arcade games. They had fixed functionality and their only task was to generate display for 2D games. Generating display required computing values for a large number of pixels. The CPU took a long time to perform this computation, which was a hurdle for real-time rendering of display necessary for games. Therefore, GPUs emerged as a solution to this problem. Gradually, they were enriched to support 3D graphics and later various graphics operations like geometry transformations and pixel-shading functions. They still provided a fixed functionality and were not programmable. The first GPU with programmmable shading capability was Nvidia GeForce 3 (NV20) that allowed programmers to write small custom shaders which were run for every pixel in the image or every vertex in the graphics model. Over time, they started supporting more complex shaders with lengthy loops and floating point computation, and eventually evolved into flexible data-parallel graphics engines. Since graphics computation involved a large number of matrix and vector operations, researchers realized their computational abilities and used the shader engine to accelerate operations like matrix multiplication and LU factorization [24]. The computation still had to be mapped on to graphics primitives, and hence, languages like Sh [47], Brook [9] and Accelerator [65] emerged to provide a general-purpose interface to GPUs. The languages still performed redundant graphics computation, and therefore, native support for general-purpose GPU computing developed with languages like CUDA [51] by Nvidia and OpenCL [63] by the Khronos Group. Ever since, the use of GPUs for generalpurpose computing has been growing exponentially.

GPUs present a data-parallel compute platform, where a large number of threads exe-

cute the same sequential program. This is useful when the same computation needs to be performed on a large amount of data, as happens to be the case in graphics applications where the same computation is repeated on a large number of pixels and vertices. With frequency scaling no longer possible, CPUs have reached their limits on single-thread performance, and the only way to achieve significant performance is through parallelism. GPUs with their inherently parallel model of computation provide a viable alternative. With burgeoning amounts of data everywhere, GPUs are well-suited to process the data with their high throughput and energy efficiency.

An interesting observation is that, unlike CPUs, which emerged from theoretical models like lambda calculus and Turing machines through decades of research, GPUs started out as an engineering solution to display graphics, and only recently have gained interest from researchers. This means there is a general lack of formal models backing the GPU architecture and the languages supported by GPUs. The model of computation presented by GPUs needs to be studied carefully to understand its capabilities and limitations. The use of GPUs for serious applications also entails the need to ensure that GPU programs produce correct and reliable results. This requires a new set of formal tools and techniques which can ensure correctness of GPU computation. Unlike CPU programs where the programmer can be completely oblivious of the underlying platform due to the sophisticated compiler and hardware technology developed over the years, the GPU compiler and hardware are still catching up and the programmer needs to be aware of the subtleties of the GPU architecture and must carefully tune various execution parameters to achieve significant performance gain. In general, there is need for better language, tool and hardware support to make GPU programming as easy, reliable and performant as programming for CPUs.

A closely related architecture to GPUs is that of vector processors, where a single thread simultaneously operates on *vectors* or arrays of data, also known as the Single Instruction Multiple Data (SIMD) model [19]. This is unlike the GPU model where a large number of threads operate on scalar data. Vector processors have been studied well in the literature, and a large number of automatic optimizations have been developed to optimize sequential code using vector instructions. The vector processors, however, present instruction-level parallelism, where each instruction is executed in parallel for thousands of data elements. In comparison, GPUs present parallelism at the granularity of whole programs, where the complete program is executed in parallel. The distinction between the two architectures hasn't been studied formally, however, and performance and programmability implications of the two architectures need to be explored further.

Significant research has been devoted to advancing tool support for GPUs in recent years. A large number of compiler optimization frameworks have been explored [12, 76, 64, 66, 75, 6, 23, 31]. These frameworks take unoptimized CUDA or OpenCL programs and optimize performance through various techniques like transforming data-layout for arrays and data-structures, explicitly caching data into on-chip fast memory, transforming thread-geometry etc. A large number of auto-tuning techniques have emerged to enable programmers to automatically identify best execution configuration [69, 45, 38, 13, 46, 74]. These techniques empirically explore the space of values for various parameters like the data-layout representation, the thread-coarsening factor and the launch parameters like block-size and grid-size.

Various domain-specific languages have emerged with GPU back-ends that automatically generate code for GPUs, for example Halide [55] for image-processing pipelines and TensorFlow [2] for machine learning. Many generic languages are also being used to generate GPU code, including legacy languages like OpenMP [41] or C [68] and new languages like pragma-based OpenACC [71]. There has been some research to improve the GPU hardware for better utilizing the memory subsystem and for balancing thread-level parallelism with cache and memory utilization [57, 50, 34, 61, 39, 56, 32]. Finally, there has been some research on verifying correctness of GPU programs for issues like data-races and barrier divergence [44, 43, 8, 21]. These techniques employ static and dynamic analyses to detect concurrency issues and in some cases verify absence of bugs. Despite this body of research, a large number of challenges remain, and we have only taken first steps towards building robust tools for efficient GPU programming.

# 1.1 Challenges with GPU Programming

Almost every field of science today is overwhelmed with data, ranging from medical imaging to cosmological simulations [35]. With increase in sophistication, richer data is produced at a faster pace by the modern systems, and hence, GPU acceleration is necessary to analyze the data. Also, the needs of the computation are specific to each domain, which existing GPU-based frameworks do not cater to. The existing frameworks themselves are often complex and not well-maintained, which leads domain scientists to write their own GPU programs. Efficient GPU programming is an art, however, and non-expert programmers find it difficult to write correct and efficient GPU programs.

There are multiple reasons for this. First, there are a large number of parameters that need to be tuned in order to get good performance. The space of values is large and the the combinations of values that need to be explored is overwhelming. While auto-tuning frameworks have been developed to cater to this problem, not all choices for parameters are correct, and subtle errors can enter the program when the parameters are modified. These errors can be difficult to debug and none of the existing tools ensure correctness for parameter tuning.

Second, tuning parameters may not be sufficient to achieve good performance. GPUs are sensitive to how programs interface with the memory subsystem. If the programmer is not careful and uses poor memory access patterns, the memory subsystem may get congested and take a long time to respond to program's requests, bringing down the overall performance. While this problem has been well-documented, only way to identify such issues is to actually execute the program and observe performance bottlenecks at run-time. There is a need for tools that report performance issues at compile-time or as the programmer writes the GPU program.

Third, while the compiler technology has made significant strides at automatically optimizing CPU programs, this is not true for GPU programs. The GPU programmer has to manually rewrite parts of the program to improve performance which leads to code with poor readability and maintainability. There are two primary problems with automatic optimization for GPUs. First, non-trivial transformations like loop-tiling or loop-reordering are

necessary to improve performance which are difficult to implement correctly. Many existing prototypes have tried implementing these transformations without successful transition to practice. It is also not clear when these techniques are applicable and how the programmer can direct tools to implement necessary optimizations. Second, while a few formal approaches have been developed to systematically optimize GPU programs, they require the programs to be well-structured with well-defined loop bounds and array indices. This prevents their applicability to general GPU programs, which are easier to write for non-expert programmers. Hence, we need tools for robust optimization of general GPU programs.

Finally, there is a need for newer languages with better support from hardware to make GPU programming robust and efficient at a larger scale. We need new languages with semantics that are easy to reason with, both manually and automatically. We need richer controls from the hardware, for the compiler to robustly optimize GPU programs. Lastly, we need program representations which are easy to analyze and manipulate within the compiler.

# 1.2 Structured Parallelism

A key feature that distinguishes GPU programming model from other concurrency models is that there is *structure* or regularity in the parallelism offered by the model. While there are a large number of threads executing, the threads execute the same sequential program and their executions are often correlated, especially for *regular* programs where the control flow and memory access patterns are independent of input data. For instance, the programs often operate on matrices and vectors, where each thread is assigned a row, column or a cell in the matrix and it performs the same operation. Further, there is structure within the execution of threads, when loops are present in the program and each iteration of the loop performs a similar operation. For example, when a thread is assigned a row in a matrix, it iterates over the cells of the row while repeating the same operation. This repeating pattern within a thread and across threads is very useful for compile-time analysis and optimization.

Our work formally identifies this repeating pattern for general GPU programs, both across the execution of multiple threads and within the execution of a single thread. While identifying the pattern exactly is difficult, an over-approximation is good enough to establish various properties of the programs, for instance, whether a program uses poorly performing memory access patterns (also known as uncoalesced accesses), or whether modifying an execution parameter is valid and leads to a correct program. We use abstraction-based static analyses to identify these properties. We have defined a model for GPU programs in Chapter 2, where we formalize the full-functional behavior of GPU programs while making reasonable simplifications. We use this model to formally describe our analyses. We define abstract domains that identify the information required by the analyses and associate an abstract state and abstract semantics with each analysis to describe how the analyses execute on a GPU program. We rely on the formal model to reason about the correctness of the analyses and to ensure all corner cases are covered. Further, the abstraction-based approach helps filter out the relevant information from program state, which enables the analysis to be light-weight and to scale to large programs. We have also developed a framework to implement such analyses in LLVM, a popular state-of-the-art open-source compiler, which we describe in Chapter 3.

We use the framework to define three static analyses. The first static analysis determines whether a GPU program consists of poorly performing memory access patterns. In a GPU program, threads execute instructions often in lock-step. When threads execute access to global memory locations in the program, instead of fetching the memory location for each thread individually, the GPU hardware groups together locations accessed by multiple threads into a few memory transactions. If threads access memory locations within the same memory block, a single transaction is sufficient. However, if threads access distant locations, multiple transactions are necessary, which leads to poor performance. Such accesses are referred to as uncoalesced accesses. Our static analysis identifies uncoalesced accesses by computing the stride or the distance between memory locations accessed by consecutive threads. For coalesced accesses, where the accesses lie within a single memory block, the stride is often constant with value one and is computable at compile-time. Therefore, our analysis identifies all such accesses with a stride of value at most one, and reports the remaining accesses as uncoalesced. Our analysis performs fairly well with a false positive rate of 38%, while identifying 111 uncoalesced accesses in Rodinia, an academic benchmark suite of GPU programs. We describe this analysis further in Chapter 4.

Our second analysis checks if modifying an execution parameter *block-size* is valid. The threads in a GPU program are organized in a two-level hierarchy, where a group of threads forms a *thread-block* and group of thread-blocks forms the overall *thread-grid*. The *block-size* determines the number of threads per thread-block and is often adjusted to improve the overall utilization of cores within the GPU. Modifying block-size is however not valid, if the computation performed by the program depends on the value of block-size and changing the value leads to incorrect results. Our analysis checks if any of the block-size dependent values, including block-size itself, *flow* into the final result computed by each thread. If not, the program is *block-size independent* and modifying block-size is valid. The block-size dependent values are often used in a regular pattern which allows the analysis to prove block-size dependence for a large number of programs. We identify 35 procedures to be block-size independent in Nvidia's SDK samples. We describe this analysis further in Chapter 5.

Our final analysis determines the potential to utilize hardware cache to automatically improve performance of a GPU program. The analysis identifies accesses that benefit from cache reuse across iterations of a loop within the execution of a thread. It determines the distance between memory locations accessed by an access in consecutive iterations of a loop, and if the distance is small, the access is considered *cache reusable*. A program with one or more cache reusable accesses can benefit from cache reuse. On-chip cache reuse to utilize locality within each thread is often relinquished for thread-level parallelism, where the simultaneous execution of a large number of threads leads to cache contention, and therefore, poor utilization. However, if there is significant locality within a thread, identified by the presence of cache reusable accesses in the program, and very little locality across threads, identified by the presence of uncoalesced accesses, then giving up thread-level parallelism for improved cache reuse is beneficial. We have implemented this optimization in LLVM and observe an average  $1.3\times$  speedup in benchmark performance against the base compiler without our optimization. We describe the analysis to determine cache reuse and our optimization

to improve cache utilization in Chapter 6.

Finally, this thesis makes the following contributions to the state-of-the-art in analysis and optimization of GPU programs:

- (1) We present the first *light-weight formal* analyses and optimization for *general* GPU programs. Light-weight techniques are necessary to scale to large programs and to allow usage at compile-time. A formal approach to define analyses and optimizations helps reason about correctness. Applicability to general GPU programs makes these techniques widely applicable.

- (2) We have implemented the approach in LLVM, a popular open-source compiler. The implementation is modular and well-developed and tested on various benchmarks. The build is completely automated and the tool is easy to install on a new system.

# 1.3 Organization

The thesis is organized as follows. Chapter 2 presents a background on GPU programming and a formal model for functional behavior of GPU programs. Chapter 3 presents a framework to define abstraction-based static analyses. Chapter 4 presents our static analysis to detect uncoalesced accesses. Chapter 5 presents an analysis to verify block-size independence of GPU programs. Chapter 6 presents an analysis to identify intra-thread cache reuse across loop iterations within a GPU program and our optimization to improve cache utilization. Finally, Chapter 7 presents some concluding remarks.

# Chapter 2

# **Fundamentals of GPU Programming**

GPUs have emerged as a popular data-parallel architecture and programming languages like CUDA [51] and OpenCL [63] have been developed to support these devices. GPUs present an interesting computation model where a large number of threads execute the same sequential program and the execution for threads is distinguished via unique identifiers assigned to each thread. This leads to a lot of regularity in the parallelism offered by the model, which makes GPU programs amenable to analysis and performance optimization, unlike general concurrent programs.

GPU computing has emerged only recently, and therefore, the programming models have not been studied formally. There is previous work on modeling correctness issues like data-races in GPU programs [8, 43, 44]. There is, however, scope to model other features like performance and correctness of transformations. A formal model forms the basis for correct and efficient analyses and transformations. Therefore, good formal models for GPU programs are required, and in our work we formalize one such model.

This chapter presents the fundamentals of GPU programming. We first present a brief background on the programming model and the architecture for GPUs (Section 2.1). We describe how GPU programs are written in popular languages like CUDA and OpenCL and how the programs are executed on GPUs. We illustrate this further using an example (Section 2.2), and use the example to introduce our formalization. We then describe our formal model that captures the functional and performance behavior of GPU programs (Section 2.3). The model serves as the basis for various analyses which we describe in subsequent chapters. Even otherwise, the model precisely represents various aspects of GPU programming, which is useful in understanding the general programming model. We finally present some limitations of our formalization (Section 2.4).

# 2.1 Background

We present a brief background on GPUs and their programming model. GPUs present a highly *data-parallel* architecture, where a large number of threads execute the same sequence of instructions. This architecture is useful for applications where the same compu-

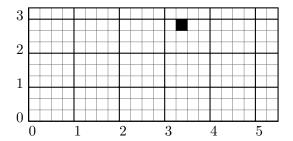

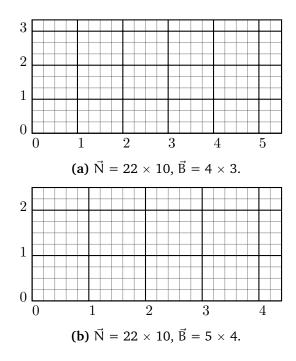

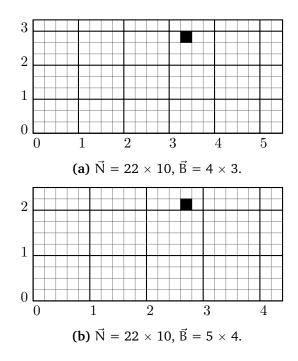

**Figure 2.1:** An example 2-dimensional thread-grid with  $22 \times 10$  total threads (grid-size) and  $4 \times 3$  threads per block (block-size). Each solid block represents a thread-block, while each cell represents a thread. The values represent the block-id along respective dimensions. The darkened cell corresponds to a thread with block-id (3,2) and thread-id (1,2).

tation needs to be performed on a large amount of data. The data-parallel nature of the GPU architecture enables numerous optimizations which help GPU applications scale, while traditional multi-threaded applications often do not scale with increase in the amount of resources. Two prominent optimizations include (a) *parallelism-based latency hiding*, where the execution of multiple parallel threads is used to hide the latency of compute and memory operations, and (b) *memory access coalescing*, where memory accesses by multiple threads are coalesced or grouped together into a few memory transactions, significantly reducing the overall access latency. We present the GPU programming model in Section 2.1.1, followed by some insight into the GPU architecture in Section 2.1.2. Note that, we follow the CUDA terminology here. The other popular model, OpenCL, uses a slightly different terminology, though the concepts are similar in both models.

#### 2.1.1 GPU Programming Model

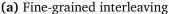

GPUs follow a Single Instruction Multiple Threads (SIMT) programming model, where a large number of threads execute the same sequence of instructions. The threads are organized in a two-level hierarchy: a group of threads form a thread-block and a set of thread-blocks form a thread-grid. Each thread in the grid is assigned a *thread-id* that uniquely identifies the thread within the block, and a *block-id* that uniquely identifies its block within the grid. Further, the grid can be multi-dimensional with up to three dimensions, and each thread is assigned a multi-dimensional thread-id and a block-id. These dimensions map naturally to 2D and 3D images which represent a traditional application domain for GPU computing. The overall size of the grid and blocks is defined by multi-dimensional vectors *grid-size* and *block-size*, respectively, both of which are initialized when the execution of the GPU program is initiated. Figure 2.1 presents an example thread-grid.

The sequence of instructions executed by the threads in a GPU program is often called the *kernel*. The kernel is essentially a sequential method with special read-only variables for thread-id (tid), block-id (bid), grid-size (gdim) and block-size (bdim). The variables tid and bid are instantiated with a distinct value for each thread, which helps distinguish the

```

__global__ void Fan1(float *M, float *A, int N, int i) {

int x = tid.x + bid.x * bdim.x;

if(x >= N-i-1) return;

M[N*(x+i+1)+i] = A[N*(x+i+1)+i] / A[N*i+i];

__global__ void Fan2(float *M, float *A, float *B, int N, int i) {

int x = tid.x + bid.x * bdim.x;

int y = tid.y + bid.y * bdim.y;

if(x >= N-i-1) return;

if(y >= N-i) return;

A[N*(x+i+1)+(y+i)] -= M[N*(x+i+1)+i] * A[N*i+(y+i)];

if(y == 0) {

B[x+i+1] -= M[N*(x+i+1)+(y+i)] * B[i];

}

int ForwardSub(float *m, float *a, float *b, int N) {

cudaMemcpy(M, m, N*N, 'CPUtoGPU');

cudaMemcpy(A, a, N*N, 'CPUtoGPU');

cudaMemcpy(B, b, N, 'CPUtoGPU');

for (int i=0; i<(N-1); i++) {</pre>

Fan1 <<< N, 512 >>> (M, A, N, i);

Fan2 << <(N, N), (512, 512) >>> (M, A, B, N, i);

cudaMemcpy(m, M, N*N, 'GPUtoCPU');

cudaMemcpy(a, A, N*N, 'GPUtoCPU');

cudaMemcpy(b, B, N, 'GPUtoCPU');

}

```

**Figure 2.2:** Forward Substitution subroutine in a Gaussian elimination application. Methods Fan1() and Fan2() are GPU kernels and execute on GPU, while method ForwardSub() runs on the CPU. Here, tid, bid and bdim refer to thread-id, block-id and block-size, respectively. Method cudaMemcpy() copies data between CPU and GPU.

execution of threads. The kernel is embedded as a subroutine within the GPU application and is launched via a function call to the kernel from sequential code that runs on the CPU. Figure 2.2 shows an example GPU application. Note that, methods Fan1() and Fan2() representing GPU kernels are called from the ForwardSub() method which runs on the CPU. Further, the method calls to Fan1 and Fan2 are qualified by parameters within <<<...>>> enclosure which represent the grid-size and block-size for the grid of threads for which the GPU kernel is executed. We describe more details about the program in Section 2.2. Lastly, the GPU kernels can make calls to other GPU kernels like any other function call. A distinction is often made between *global* kernels, which are called only from CPU code, and the *device* kernels, which are called only from GPU code *i.e.* other global and device kernels.

Each thread in a GPU program has access to different memory spaces. The variables in the kernel are qualified by the memory space they reside in, and the threads access the

corresponding memory space for each variable to fetch/write data to the variable. We briefly describe the different memory spaces here:

- Local memory: This memory space is private to each thread and the data stored in this space is not visible to other threads. Each thread has a separate copy of variables in this space, and hence, the same local variable in different threads might store different values. This space is primarily used for performing local computations within each thread.

- Shared memory: This memory space is shared across threads within a thread-block and a single copy of variables in this space is visible to all threads within the block. However, each block has a separate copy of variables. This space is used to share data between threads within a block. It provides a fast look-up and is often used as a user-managed cache.

- Global memory: This memory space is shared across all threads in the grid and a single copy of variables is visible to all threads. The space acts as an interface between the CPU and GPU, and stores the data on which a GPU kernel performs computation. During a GPU kernel execution, the data is first copied from CPU memory into global memory, then the kernel execution is initiated and operations are performed on the data in global memory, and after the execution is completed, the output data, representing the result of the kernel execution, is copied back from global memory to CPU memory.

- Constant memory: This is a special memory space that stores read-only data. The

space is similar to global memory and a single copy of variables is visible to all threads.

However, since it is read-only, it benefits greatly from caching and provides a fast readonly alternative to global memory.

We next describe some common primitives used to synchronize threads and share data between them. We describe two kinds of primitives: *barriers* that ensure that all threads in a block reach a program point before they continue further execution, and *atomic* operations that ensure exclusive access to a memory location by each thread for the duration of the operation.