Xilinx ISE Tips

CSE 372 (Spring 2007): Digital Systems Organization and Design Lab

This page contains several useful tips for using Xilinx ISE and related tools.

Setting top module for synthesis

In the Sources hierarchy in ISE, only one module can be set as the "top" module for synthesis and implementation. When working with a hierarchy of modules, you may not always want the module at the top of the hierarchy to be the module for synthesis. For example, if you have created interfaces for several modules but have not finished implementing them all yet, you can set the module you are currently working on as the top module, then make sure it synthesizes and implements correctly before moving on to other modules.

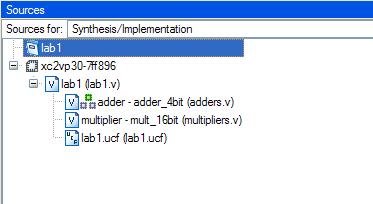

The adder_4bit module is set as the top module, because the other modules in the hierarchy are not ready for synthesis.

When generating a programming file to download to your FPGA, the module at the top of the hierarchy (with a .ucf file associated with it) should be set as the top module.

Missing source files

After creating a new source file for your project or adding an existing source file to your project in ISE, the file may not immediately appear in the Sources hierarchy (or it may "disappear" once you save it). Locate the file by choosing different options from the "Sources for" drop-down box; for example, after adding a new Verilog module (.v) file, it may appear under "Behavioral Simulation," instead of under "Synthesis/Implementation" as expected. Once you have found the new source file, right-click on it and choose Properties. Change the association to the proper value: "Synthesis/Imp + Simulation" for .v files containing Verilog design modules, "Simulation Only" for .tf or .v files containing test fixtures, and "Synthesis/Implementation Only" for .ucf files. The new source file should now appear in the expected location in the Sources hierarchy.

Cleanup project files

If you are receiving any strange warning or error messages in ISE, old synthesis and implementation result files that are present in your project directory may be causing them. To clear these old files from your project directory (and hopefully clear up any unusual behavior), choose Project -> Cleanup Project Files from the main menu bar, then click Yes on the dialog box that appears. All of your source files will remain, but any files generated by the synthesis and implementation processes will be removed.

Verilog syntax check failed for no reason

Sometimes checking syntax on a perfectly fine verilog file just fails, with no specific error given. The cause is that the Xilinx project doesn't recognize the file being there. The solution is to remove the verilog file from the project (by removing all the modules it contained), and adds the source file back in.