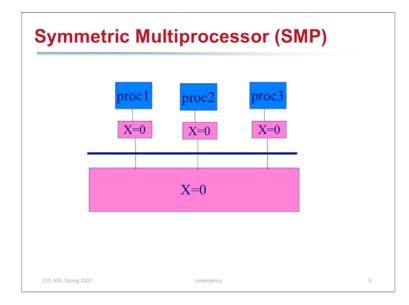

# Cache/Memory Coherence and consistency Replicated shared data and concurrent access by many processors Coherence: every cache/processor must have a coherent view of memory Informally, memory is coherent if the value returned by a read op is always the value that the programmer expects, e.g., read mostly recently written value If P writes X to A, then reads A, if no other proc writes A, then P reads X If P1 writes X to A, and no other processor writes to A, then P2 will eventually read X from A. If P1 writes X to A and P2 writes X to A then every processor will either

- o If P1 writes X to A, and P2 writes Y to A, then *every* processor will either read X then Y, or Y then X, but all will see the writes in the same order.

- Consistency: memory consistency model tells us when writes to *different* locations will be seen by readers.

CIS 505, Spring 2007

onsistency

# **Consistency models**

- Strict consistency

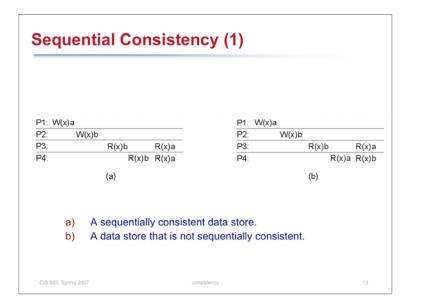

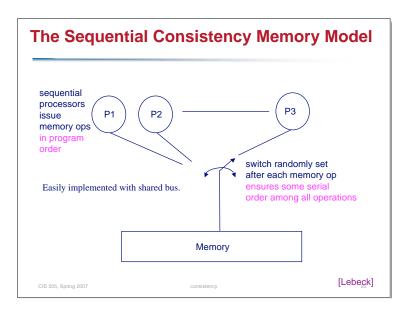

- Linearizability and sequential consistency

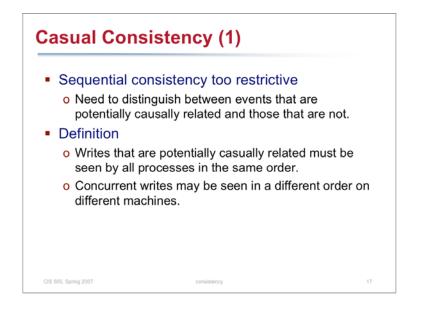

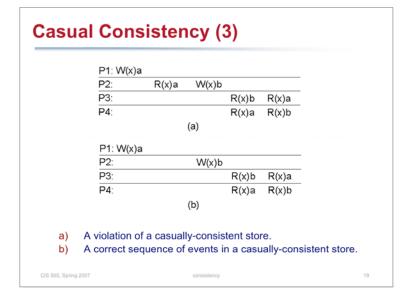

- Causal consistency

- FIFO consistency

### Other weaker notions:

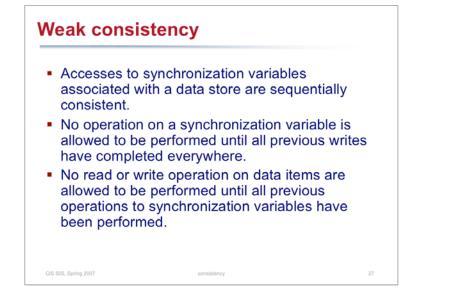

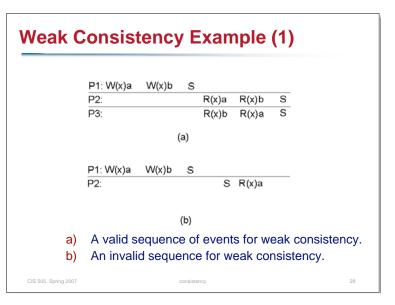

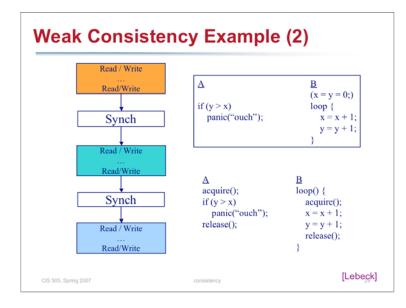

- Weak consistency

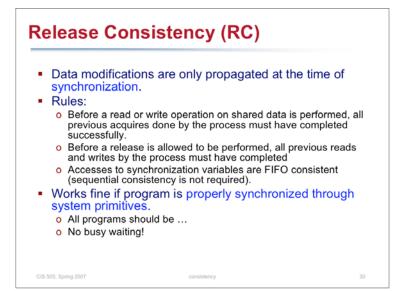

- Release consistency

- Entry consistency

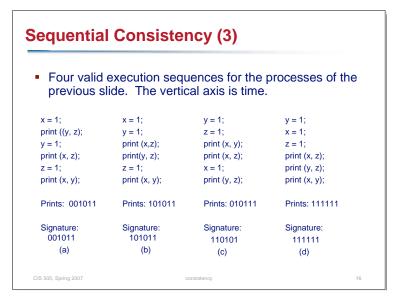

| Process P1         Process P2         Process P3           x = 1;         y = 1;         z = 1;           print (y, z);         print (x, z);         print (x, y); |                                 |                      |            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|------------|--|

| print ( y, z); print (x, z); print (x, y);                                                                                                                          | Process P1                      | Process P2           | Process P3 |  |

| <ul> <li>Three concurrently executing processes.</li> </ul>                                                                                                         |                                 |                      | ,          |  |

|                                                                                                                                                                     | <ul> <li>Three conce</li> </ul> | urrently executing p | rocesses.  |  |

| Possible ex                                   | ecution sequence                                                                             | S             |

|-----------------------------------------------|----------------------------------------------------------------------------------------------|---------------|

| <ul> <li>How many o<br/>o 720 (6!)</li> </ul> | distinct sequences are the                                                                   | ere?          |

| o Start with x<br>them are v                  | =1: 120 (5!), not all possible,<br>alid                                                      | just 30 of    |

| o 30 x 3 = 90                                 | valid execution sequences                                                                    |               |

| the outputs                                   | only consider outputs as con-<br>of P1, P2, P3 in that order<br>64 (2**6) signature patterns | catenation of |

| <ul> <li>Not all of</li> </ul>                | them are permitted; e.g., 00000, 00                                                          | )1001         |

|                                               |                                                                                              |               |

| CIS 505, Spring 2007                          | consistency                                                                                  | 15            |

| P1: W(x)a |       |       | W(x)c |       |       |

|-----------|-------|-------|-------|-------|-------|

| P2:       | R(x)a | W(x)b |       |       |       |

| P3:       | R(x)a |       |       | R(x)c | R(x)b |

| P4:       | R(x)a |       |       | R(x)b | R(x)c |

|           |       |       |       |       |       |

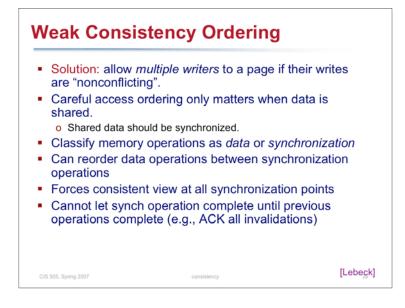

## **Grouping Operations (1)**

- Necessary criteria for correct synchronization:

- An acquire access of a synchronization variable, not allowed to perform until all updates to guarded shared data have been performed with respect to that process.

- Before exclusive mode access to synchronization variable by process is allowed to perform with respect to that process, no other process may hold synchronization variable, not even in nonexclusive mode.

- After exclusive mode access to synchronization variable has been performed, any other process' next nonexclusive mode access to that synchronization variable may not be performed until it has performed with respect to that variable's owner.

## **Grouping Operations (2)**

P1: Acq(Lx) W(x)a Acq(Ly) W(y)b Rel(Lx) Rel(Ly) P2: Acq(Lx) R(x)a R(y) NIL

P3: Acq(Ly) R(y)b

• Figure 7-10. A valid event sequence for entry consistency.

22

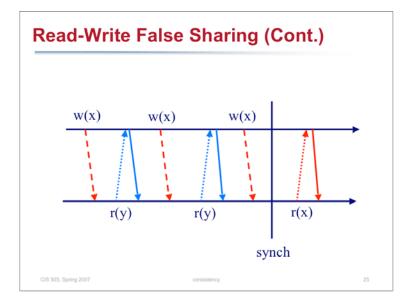

# **Motivation for Weaker Orderings**

- Sequential consistency is sufficient (but not necessary) for shared-memory parallel computations to execute correctly

- Sequential consistency is slow for paged DSM systems.

- Processors cannot observe memory bus traffic in other nodes.

- o Even if they could, no shared bus to serialize accesses.

- o Protection granularity (pages) is too coarse.

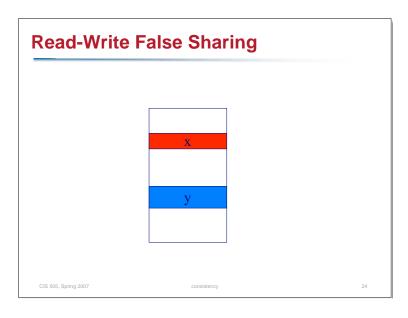

- Basic problem: the need for exclusive access to pages leads to false sharing.

- Causes a "ping-pong effect" if multiple writers to the same page.

```

3 505, Spring 2007

```

[Chase] 23

| · · · ·         | nsistency models not using synchronization operations.<br>dels with synchronization operations.                                               |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Consistency     | Description                                                                                                                                   |

| Strict          | Absolute time ordering of all shared accesses matters.                                                                                        |

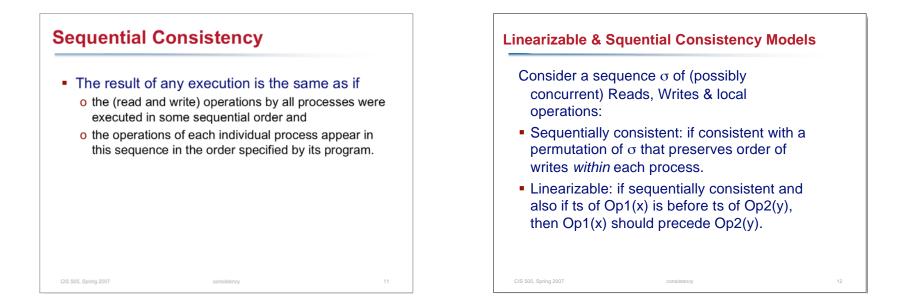

| Linearizability | All processes must see all shared accesses in the same order. Accesses are furthermore ordered<br>according to a (nonunique) global timestamp |

| Sequential      | All processes see all shared accesses in the same order. Accesses are not ordered in time                                                     |

| Causal          | All processes see causally-related shared accesses in the same order.                                                                         |

| FIFO            | All processes see writes from each other in the order they were used. Writes from different<br>processes may not always be seen in that order |

|                 | (a)                                                                                                                                           |

| Consistency     | Description                                                                                                                                   |

| Weak            | Shared data can be counted on to be consistent only after a synchronization is done                                                           |

| Release         | Shared data are made consistent when a critical region is exited                                                                              |

| Entry           | Shared data pertaining to a critical region are made consistent when a critical region is entered.                                            |