|                                                                           | BSR<3:0> |         |                   | Data Memory Ma    | p                                      | When a = o:<br>The BSR is ignored and the                                |

|---------------------------------------------------------------------------|----------|---------|-------------------|-------------------|----------------------------------------|--------------------------------------------------------------------------|

| Data Memory                                                               | = 0000   | Bank 0  | 00h<br>FFh        | Access RAM<br>GPR | 000h<br>05Fh \<br>060h<br>0FFh         | Access Bank is used.<br>The first 128 bytes are<br>general purpose RAM   |

|                                                                           | = 0001   | Bank 1  | 00h<br>FFh        | GPR               | 100h                                   | (from Bank 0).<br>The second 128 bytes are<br>Special Function Registers |

|                                                                           | = 0010   | Bank 2  | 00h               | GPR               | 200h                                   | (from Bank 15).<br>When a = 1:                                           |

| <ul> <li>Memory layout</li> </ul>                                         | = 0011   | Bank 3  | FFh<br>00h        | GPR               | 2FFh<br>300h                           | The BSR specifies the Bank<br>used by the instruction.                   |

| <ul> <li>Instructions in the PIC18<br/>are limited to 16 bits.</li> </ul> | = 0100   | Bank 4  | FFh<br>00h<br>FFh | GPR               | 3FFh<br>400h<br>4FFh                   |                                                                          |

| • To address the whole                                                    | = 0101   | Bank 5  | 00h               | GPR               | 500h                                   |                                                                          |

| area you would need 12<br>bit => too many.                                | = 0110   | Bank 6  | FFh<br>00h<br>FFh | GPR               | 5FFh<br>600h<br>6FFh                   | Access Bank                                                              |

| o Memory is split into 256B                                               | = 0111   | Bank 7  | 00h               | GPR               | 700h                                   | Access RAM Low 5Fh                                                       |

| banks. Only one is active.                                                | = 1000   | Bank 8  | 00h               | GPR               | 800h                                   | Access RAM High<br>(SFRs) FFh                                            |

| <ul> <li>Register types</li> </ul>                                        | = 1001   | Bank 9  | FFh<br>00h        | GPR               | 8FFh<br>900h                           |                                                                          |

| o General-purpose                                                         | = 1010   | Bank 10 | FFh<br>00h        | GPR               | 9FFh<br>A00h                           | /                                                                        |

| registers (GPR)                                                           | = 1011   | Bank 11 | FFh<br>00h        | GPR               | AFFh<br>B00h                           |                                                                          |

| <ul> <li>Special function registers<br/>(SFR)</li> </ul>                  | = 1100   | Bank 12 | FFh               | GPR               | BFFh<br>C00h                           |                                                                          |

|                                                                           | = 1101   | Bank 13 | FFh<br>00h        | CAN SFRs          | CFFh<br>D00h                           | /                                                                        |

| <ul> <li>SFR control the MCU and<br/>the peripherals.</li> </ul>          | = 1110   | Bank 14 |                   | CAN SFRs          | DFFh<br>E00h                           |                                                                          |

| CSE480/CIS700                                                             | = 1111   | Bank 15 | FFh<br>00h<br>FFh | CAN SFRs<br>SFR   | EFFh<br>F00h<br>F5Fh<br>F60h /<br>FFFh | /                                                                        |

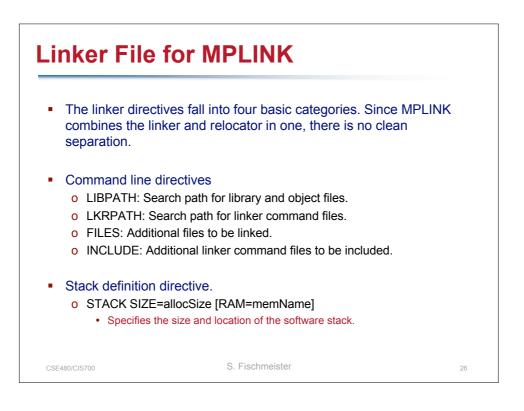

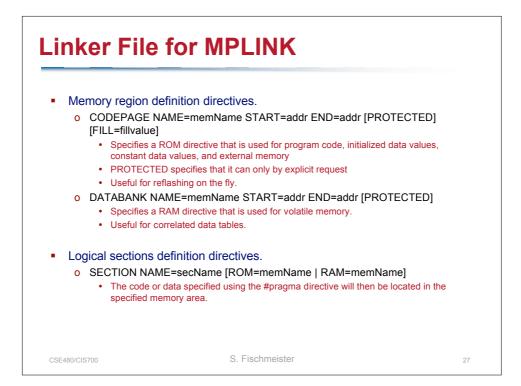

|               |                              | ker File                   |                        |           |    |

|---------------|------------------------------|----------------------------|------------------------|-----------|----|

| ІТВРАТН .     |                              |                            |                        |           |    |

| FILES c018    | i.o                          |                            |                        |           |    |

| FILES clib    |                              |                            |                        |           |    |

| FILES p18f    | 8720.lib                     |                            |                        |           |    |

| CODEPAGE      | NAME=vectors                 | START=0x0                  | END=0x29               | PROTECTED |    |

| CODEPAGE      | NAME=page                    | START=0x2A                 | END=0x1FFFF            |           |    |

| CODEPAGE      | NAME=eeprom                  | START=0x20000              | END=0x1FFFFF           | PROTECTED |    |

| CODEPAGE      | NAME=idlocs                  | START=0x200000             | END=0x200007           | PROTECTED |    |

| CODEPAGE      | NAME=config                  | START=0x300000             | END=0x30000D           | PROTECTED |    |

| CODEPAGE      | NAME=devid                   | START=0x3FFFFE             | END=0x3FFFFF           | PROTECTED |    |

| CODEPAGE      | NAME=eedata                  | START=0xF00000             | END=0xF003FF           | PROTECTED |    |

| ACCESSBANK    | NAME=accessram               | START=0x0                  | END=0x5F               |           |    |

| DATABANK      | NAME=gpr0                    | START=0x60                 | END=0xFF               |           |    |

| DATABANK      | NAME=gpr1                    | START=0x100                | END=0x1FF              |           |    |

|               |                              |                            |                        |           |    |

| DATABANK      | NAME=gpr13                   | START=0xD00                | END=0xDFF              |           |    |

| DATABANK      | NAME=gpr14<br>NAME=accesssfr | START=0xE00<br>START=0xF60 | END=0xEFF<br>END=0xFFF | DDOWDOWDD |    |

| ACCESSBANK    | NAME=accesssir               | START=0XF60                | END=0xFFF              | PROTECTED |    |

| SECTION       | NAME=CONFIG                  | ROM=config                 |                        |           |    |

| SECTION       | NAME=STARTUP                 | ROM=vectors                | // Reset and interrup  | vectors   |    |

| SECTION       | NAME=PROG                    | ROM=page                   | // main application co | ode space |    |

| SECTION       | NAME=INTHAND                 | ROM=eeprom                 | // Interrupt handlers  |           |    |

| SECTION       | NAME=DATTBL                  | ROM=eeprom                 | // Data tables         |           |    |

| STACK SIZE    | =0x100 RAM=gpr14             |                            |                        |           |    |

| CSE480/CIS700 |                              | 0 0                        | Fischmeister           |           | 28 |

| Туре                                                                     | Size    | Minimum                 | Maximum       |

|--------------------------------------------------------------------------|---------|-------------------------|---------------|

| char <sup>(1,2)</sup>                                                    | 8 bits  | -128                    | 127           |

| signed char                                                              | 8 bits  | -128                    | 127           |

| unsigned char                                                            | 8 bits  | 0                       | 255           |

| int                                                                      | 16 bits | -32,768                 | 32,767        |

| unsigned int                                                             | 16 bits | 0                       | 65,535        |

| short                                                                    | 16 bits | -32,768                 | 32,767        |

| unsigned short                                                           | 16 bits | 0                       | 65,535        |

| short long                                                               | 24 bits | -8,388,608              | 8,388,607     |

| unsigned short long                                                      | 24 bits | 0                       | 16,777,215    |

| long                                                                     | 32 bits | -2,147,483,648          | 2,147,483,647 |

| unsigned long                                                            | 32 bits | 0                       | 4,294,967,295 |

| Note 1: A plain <i>char</i> is signed<br>2: A plain <i>char</i> may be u | ,       | ult via the -k command- | line option.  |

## <section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header><section-header>

| Inline Assem                                                                                                                                                                                                | nbly                                        |          |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------|--|--|--|

| <ul> <li>An assembly section</li> </ul>                                                                                                                                                                     | on starts with _ <i>asm</i> and ends with _ | _endasm. |  |  |  |

|                                                                                                                                                                                                             | _asm<br>nop<br>_endasm                      |          |  |  |  |

| <ul> <li>Useful for optimization and implanting explicit code in the program (e.g., for traces or benchmarks).</li> <li>Should be kept to a minimum, because it turns off compiler optimization.</li> </ul> |                                             |          |  |  |  |

| CSE480/CIS700                                                                                                                                                                                               | S. Fischmeister                             | 45       |  |  |  |

CSE480/CIS700

S. Fischmeister