The concepts introduced by Protocol Boosters and Active Networks require a flexible infrastructure which has often assumed an all-software implementation of the system. The performance implications of such systems have generated a considerable amount of skepticism. The P4 project is a result of a beleif that with smart combination of dynamically reconfigurable hardware and software, good performance can be achieved.

The FPGA devices which keep the configuration in SRAM are suitable

for this concept. If some protocol processing element is necessary the

hardware implementation (i.e. FPGA configuration) can be downloaded into

the FPGA device on an as needed basis. Unnecessary modules are simply removed

from the protocol stack by disconnecting the FPGA device from the processing

stream and putting it back into the pool of the available empty devices.

Then the same device can be downloaded with some other configuration and

used for some other processing.

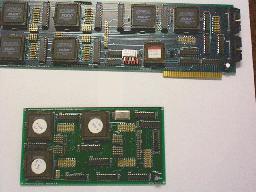

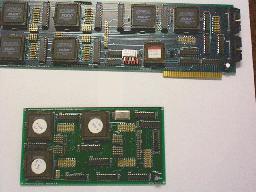

P4 board consists of the pool of the Altera Flex 8000 and Flex 10K based processing elements interconnected with the switching array which can connect or disconnect the device or reorder the devices in the processing stream. The processing is done on the pipeline basis, and the data is passed from one device to the next via FIFO buffers which interconnect them.

P4 connects to the 155Mb/s ATM link and processes the payload in a byte oriented manner. After the processing, payload is encapsulated back into the ATM cells and transmitted into the network. Though the architecture is not ATM specific, we use ATM as an undelying protocol which offers a good test environment in 100+ Mb/s regime.

The policy module which detects changes in bit error rate and inserts the FEC booster on demand is now operational.

The first version of the signalling protocol for P4 (SPP4) which synchronizes the operation of distributed P4 boards is operational.

A new, more powerful P4 board has now replaced the old P4.

I.Hadzic, J.M.Smith, "P4: A platform for FPGA implementation of Protocol Boosters", 7th International Workshop on Field Programmable Logic and Applications (FPL97), Sept. 97

I.Hadzic, J.M.Smith, W.S. Marcus, "On-the-fly Programmable Hardware for Networks", in Proceedings of Globecom 1998

I Hadzic, Signalling Protocol for P4 (SPP4), version 1.0, Techical report, MS-CIS-98-20

W.S. Marcus, I. Hadzic, A.J. McAuley, J.M. Smith, Protocol Boosters: Applying Programmability to Network Infrastructures, IEEE Communications Magazine, vol. 36, no. 10, pp. 79-83.

J.M. Smith, I. Hadzic, W.S. Marcus, ACTIVE Interconnects: Let's have some guts!, Hot Interconnects 6, August 1998, Palo Alto, California.