# CIS 501 Computer Architecture

Unit 4: Pipelining

Slides originally developed by Amir Roth with contributions by Milo Martin at University of Pennsylvania with sources that included University of Wisconsin slides by Mark Hill, Guri Sohi, Jim Smith, and David Wood.

CIS 501 (Martin): Pipelining

# Readings

• Chapter 2.1 of MA:FSPTCM

# This Unit: (Scalar In-Order) Pipelining

- Principles of pipelining

- Effects of overhead and hazards

- Pipeline diagrams

- Data hazards

- Stalling and bypassing

- Control hazards

- Branch prediction

- Predication

CIS 501 (Martin): Pipelining 2

# **Datapath Background**

CIS 501 (Martin): Pipelining 3 CIS 501 (Martin): Pipelining 4

1

#### Recall: The Sequential Model

- Basic structure of all modern ISAs

- Processor logically executes loop at left

- Program order: total order on dynamic insns

- Order and **named storage** define computation

- Convenient feature: program counter (PC)

- Insn itself at memory[PC]

- Next PC is PC++ unless insn says otherwise

- Atomic: insn X finishes before insn X+1 starts

- Can break this constraint physically (pipelining)

- But must maintain illusion to preserve programmer sanity

5

CIS 501 (Martin): Pipelining

#### Single-Cycle Datapath

- Single-cycle datapath: true "atomic" fetch/execute loop

- Fetch, decode, execute one complete instruction every cycle

- "Hardwired control": opcode to control signals ROM

- + Low CPI: 1 by definition

- Long clock period: to accommodate slowest instruction

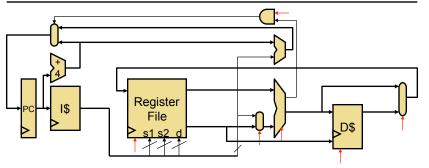

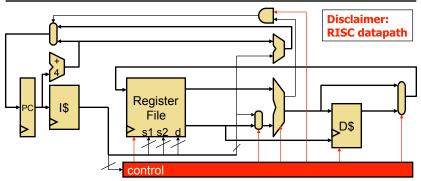

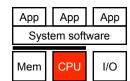

#### Datapath and Control

- Datapath: implements execute portion of fetch/exec. loop

- Functional units (ALUs), registers, memory interface

- **Control**: implements decode portion of fetch/execute loop

- Mux selectors, write enable signals regulate flow of data in datapath

- Part of decode involves translating insn opcode into control signals

CIS 501 (Martin): Pipelining 6

#### Multi-Cycle Datapath

- Multi-cycle datapath: attacks slow clock

- Fetch, decode, execute one complete insn over multiple cycles

- Micro-coded control: "stages" control signals

- Allows insns to take different number of cycles (main point)

- ± Opposite of single-cycle: short clock period, high CPI (think: CISC)

CIS 501 (Martin): Pipelining 7 CIS 501 (Martin): Pipelining 8

#### Single-cycle vs. Multi-cycle Performance

- Single-cycle

- Clock period = 50ns, CPI = 1

- Performance = **50ns/insn**

- Multi-cycle has opposite performance split of single-cycle

- + Shorter clock period

- Higher CPI

- Multi-cycle

- Branch: 20% (3 cycles), load: 20% (5 cycles), ALU: 60% (4 cycles)

- Clock period = 11ns, CPI = (20%\*3)+(20%\*5)+(60%\*4) = 4

- Why is clock period 11ns and not 10ns?

- Performance = 44ns/insn

- Aside: CISC makes perfect sense in multi-cycle datapath

CIS 501 (Martin): Pipelining

#### Latency vs. Throughput Revisited

|          | insn0.fetch, | dec, exec |                        |           |            |  |  |  |

|----------|--------------|-----------|------------------------|-----------|------------|--|--|--|

| Single-  | cycle        |           | insn1.fetch, dec, exec |           |            |  |  |  |

|          | insn0.fetch  | insn0.dec | insn0.exec             |           |            |  |  |  |

| Multi-cy | ycle         |           | insn1.fetch            | insn1.dec | insn1.exec |  |  |  |

- Can we have both low CPI and short clock period?

- Not if datapath executes only one insn at a time

- Latency and throughput: two views of performance ...

- (1) at the program level and (2) at the instructions level

- Single instruction latency

- Doesn't matter: programs comprised of billions of instructions

- Difficult to reduce anyway

- Goal is to make programs, not individual insns, go faster

- Instruction throughput → program latency

- Key: exploit inter-insn parallelism

# **Pipelining Basics**

CIS 501 (Martin): Pipelining 10

#### **Pipelining**

|         | insn0.fetch | insn0.dec   | insn0.exec |             |           |            |

|---------|-------------|-------------|------------|-------------|-----------|------------|

| Multi-c | ycle        |             |            | insn1.fetch | insn1.dec | insn1.exec |

|         |             |             |            | 1           |           |            |

|         | insn0.fetch | insn0.dec   | insn0.exec |             |           |            |

| Pipelin | ed          | insn1.fetch | insn1.dec  | insn1.exec  |           |            |

- Important performance technique

- Improves instruction throughput rather instruction latency

- Begin with multi-cycle design

- When insn advances from stage 1 to 2, next insn enters at stage 1

- Form of parallelism: "insn-stage parallelism"

- Maintains illusion of sequential fetch/execute loop

- Individual instruction takes the same number of stages

- + But instructions enter and leave at a much faster rate

· Laundry analogy

CIS 501 (Martin): Pipelining 11 CIS 501 (Martin): Pipelining 12

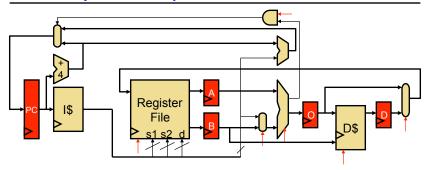

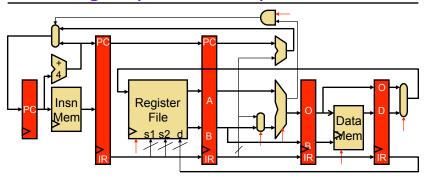

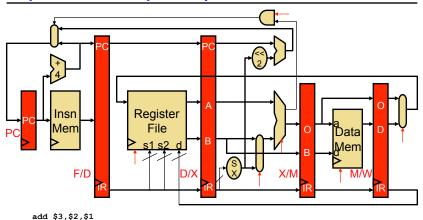

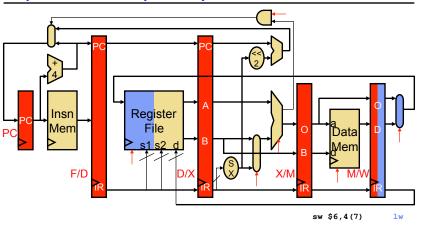

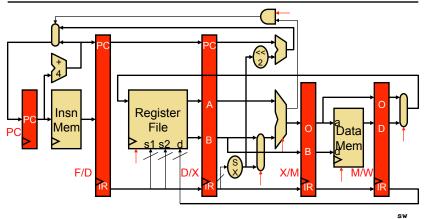

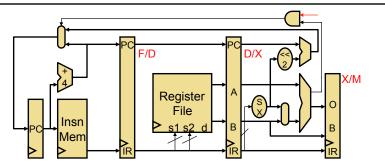

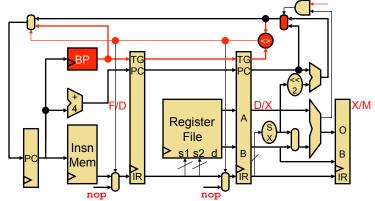

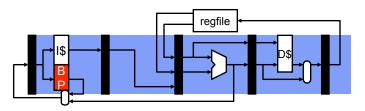

#### Five Stage Pipelined Datapath

- Temporary values (PC,IR,A,B,O,D) re-latched every stage

- Why? 5 insns may be in pipeline at once with different PCs

- Notice, PC not latched after ALU stage (not needed later)

- **Pipelined control**: one single-cycle controller

- Control signals themselves pipelined

CIS 501 (Martin): Pipelining

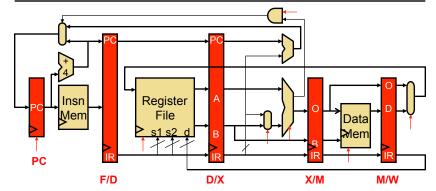

#### **Pipeline Terminology**

- Five stage: Fetch, Decode, eXecute, Memory, Writeback

- Nothing magical about 5 stages (Pentium 4 had 22 stages!)

- Latches (pipeline registers) named by stages they separate

- PC, F/D, D/X, X/M, M/W

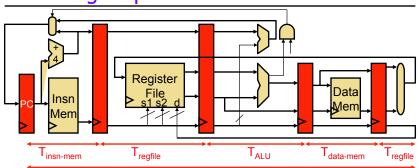

#### Five Stage Pipeline Performance

- **Pipelining**: cut datapath into N stages (here five) T<sub>singlecycle</sub>

- One insn in each stage in each cycle

- + Clock period = MAX( $T_{insn-mem}$ ,  $T_{regfile}$ ,  $T_{ALU}$ ,  $T_{data-mem}$ )

- + Base CPI = 1: insn enters and leaves every cycle

- Actual CPI > 1: pipeline must often stall

- Individual insn latency increases (pipeline overhead), not the point

CIS 501 (Martin): Pipelining 14

# More Terminology & Foreshadowing

- Scalar pipeline: one insn per stage per cycle

- Alternative: "superscalar" (later)

- In-order pipeline: insns enter execute stage in order

- Alternative: "out-of-order" (later)

- Pipeline depth: number of pipeline stages

- Nothing magical about five

- ullet Contemporary high-performance cores have  ${\sim}15$  stage pipelines

CIS 501 (Martin): Pipelining 15 CIS 501 (Martin): Pipelining 16

#### **Instruction Convention**

- Different ISAs use inconsistent register orders

- Some ISAs (for example MIPS)

- Instruction destination (i.e., output) on the left

- add \$1, \$2, \$3 means \$1 ← \$2+\$3

- Other ISAs

- Instruction destination (i.e., output) on the right add r1,r2,r3 means r1+r2→r3

1d 8(r5),r4 means mem[r5+8]→r4

st r4,8(r5) means r4→mem[r5+8]

- Will try to specify to avoid confusion, next slides MIPS style

CIS 501 (Martin): Pipelining 17

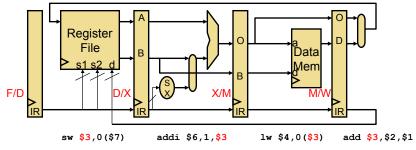

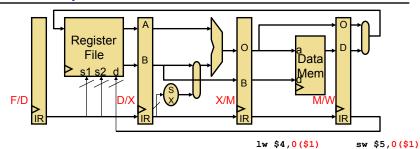

# Pipeline Example: Cycle 2

# Pipeline Example: Cycle 1

3 instructions

CIS 501 (Martin): Pipelining

18

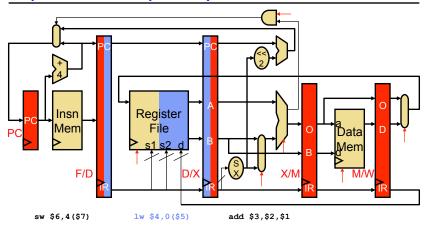

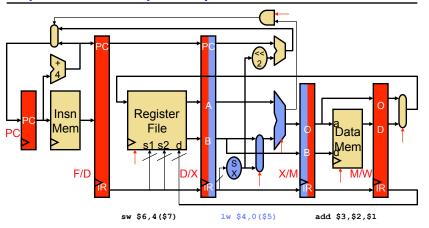

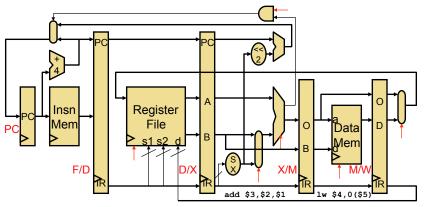

# Pipeline Example: Cycle 3

CIS 501 (Martin): Pipelining

19

CIS 501 (Martin): Pipelining

20

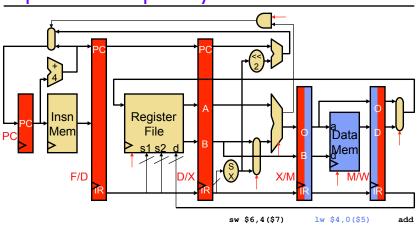

# Pipeline Example: Cycle 4

#### • 3 instructions

CIS 501 (Martin): Pipelining

# Pipeline Example: Cycle 5

CIS 501 (Martin): Pipelining 22

# Pipeline Example: Cycle 6

# Pipeline Example: Cycle 7

CIS 501 (Martin): Pipelining 23 CIS 501 (Martin): Pipelining 24

21

#### Pipeline Diagram

• Pipeline diagram: shorthand for what we just saw

Across: cyclesDown: insns

Convention: X means 1w \$4,0 (\$5) finishes execute stage and writes into X/M latch at end of cycle 4

|                 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|-----------------|---|---|---|---|---|---|---|---|---|

| add \$3,\$2,\$1 | F | D | Χ | М | W |   |   |   |   |

| lw \$4,0(\$5)   |   | F | D | X | М | W |   |   |   |

| sw \$6,4(\$7)   |   |   | F | D | Χ | М | W |   |   |

CIS 501 (Martin): Pipelining 25

#### Q1: Why Is Pipeline Clock Period ...

- ... > (delay thru datapath) / (number of pipeline stages)?

- A few reasons:

- · Latches add delay

- Extra "bypassing" logic adds delay

- Pipeline stages have different delays, clock period is max delay

- These factors have implications for ideal number pipeline stages

- Diminishing clock frequency gains for longer (deeper) pipelines

#### Example Pipeline Perf. Calculation

- Single-cycle

- Clock period = 50ns, CPI = 1

- Performance = 50ns/insn

- Multi-cycle

- Branch: 20% (3 cycles), load: 20% (5 cycles), ALU: 60% (4 cycles)

- Clock period = 11ns, CPI = (20%\*3)+(20%\*5)+(60%\*4) = 4

- Performance = 44ns/insn

- 5-stage pipelined

- Clock period = **12ns** approx. (50ns / 5 stages) + overheads

- + CPI = 1 (each insn takes 5 cycles, but 1 completes each cycle) + Performance = 12ns/insn

- Well actually ... CPI = 1 + some penalty for pipelining (next)

- CPI = **1.5** (on average insn completes every 1.5 cycles)

- Performance = 18ns/insn

- Much higher performance than single-cycle or multi-cycle

CIS 501 (Martin): Pipelining 26

#### Q2: Why Is Pipeline CPI...

- ... > 1?

- CPI for scalar in-order pipeline is 1 + stall penalties

- Stalls used to resolve hazards

- Hazard: condition that jeopardizes sequential illusion

- Stall: pipeline delay introduced to restore sequential illusion

- Calculating pipeline CPI

- Frequency of stall \* stall cycles

- Penalties add (stalls generally don't overlap in in-order pipelines)

- 1 + stall-freq<sub>1</sub>\*stall-cyc<sub>1</sub> + stall-freq<sub>2</sub>\*stall-cyc<sub>2</sub> + ...

- Correctness/performance/make common case fast (MCCF)

- Long penalties OK if they happen rarely, e.g., 1 + 0.01 \* 10 = 1.1

- Stalls also have implications for ideal number of pipeline stages

CIS 501 (Martin): Pipelining 27 CIS 501 (Martin): Pipelining 28

# **Data Dependences, Pipeline Hazards, and Bypassing**

CIS 501 (Martin): Pipelining 29 CIS 501 (Martin): Pipelining

#### Why Does Every Insn Take 5 Cycles?

- Could/should we allow add to skip M and go to W? No

- It wouldn't help: peak fetch still only 1 insn per cycle

- Structural hazards: imagine add follows 1w

#### Dependences and Hazards

- **Dependence**: relationship between two insns

- Data: two insns use same storage location

- Control: one insn affects whether another executes at all

- Not a bad thing, programs would be boring without them

- Enforced by making older insn go before younger one

- Happens naturally in single-/multi-cycle designs

- But not in a pipeline

- Hazard: dependence & possibility of wrong insn order

- Effects of wrong insn order cannot be externally visible

- Stall: for order by keeping younger insn in same stage

- Hazards are a bad thing: stalls reduce performance

30

#### Structural Hazards

#### Structural hazards

- Two insns trying to use same circuit at same time

- E.g., structural hazard on register file write port

- To fix structural hazards: proper ISA/pipeline design

- Each insn uses every structure exactly once

- For at most one cycle

- Always at same stage relative to F (fetch)

#### Tolerate structure hazards

· Add stall logic to stall pipeline when hazards occur

CIS 501 (Martin): Pipelining 31 CIS 501 (Martin): Pipelining 32

#### **Example Structural Hazard**

# 1 2 3 4 5 6 7 8 9 1d r2,0(r1) add r1,r3,r4 sub r1,r3,r5 st r6,0(r1) 1 2 3 4 5 6 7 8 9 F D X M W F D X M W F D X M W F D X M W

- **Structural hazard**: resource needed twice in one cycle

- Example: unified instruction & data memories (caches)

- Solutions:

- Separate instruction/data memories (caches)

- Redesign cache to allow 2 accesses per cycle (slow, expensive)

- Stall pipeline

CIS 501 (Martin): Pipelining 33

#### **Dependent Operations**

• Independent operations

```

add $3,$2,$1 add $6,$5,$4

```

• Would this program execute correctly on a pipeline?

```

add $3,$2,$1 add $6,$5,$3

```

What about this program?

```

add $3,$2,$1

lw $4,0($3)

addi $6,1,$3

sw $3,0($7)

```

#### **Data Hazards**

- Let's forget about branches and the control for a while

- The three insn sequence we saw earlier executed fine...

- But it wasn't a real program

- Real programs have data dependences

- They pass values via registers and memory

CIS 501 (Martin): Pipelining 34

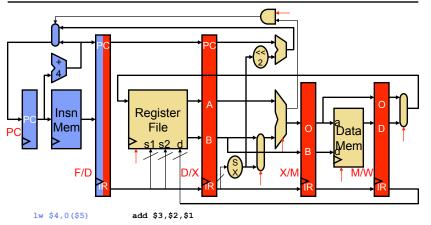

#### **Data Hazards**

- Would this "program" execute correctly on this pipeline?

- Which insns would execute with correct inputs?

- add is writing its result into \$3 in current cycle

- 1w read \$3 two cycles ago → got wrong value

- addi read \$3 one cycle ago → got wrong value

- sw is reading \$3 this cycle → maybe (depending on regfile design)

#### Memory Data Hazards

- Are memory data hazards a problem for this pipeline? No

- 1w following sw to same address in next cycle, gets right value

- Why? Data mem read/write always take place in same stage

- Data hazards through registers? Yes (previous slide)

- Occur because register write is three stages after register read

- Can only read a register value three cycles after writing it

CIS 501 (Martin): Pipelining 37

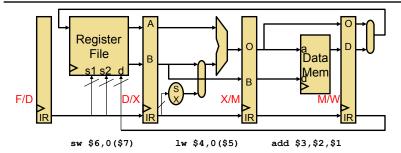

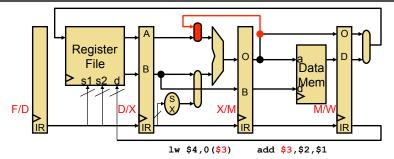

# Reducing Data Hazards: Bypassing

#### Bypassing

- Reading a value from an intermediate (µarchitectural) source

- Not waiting until it is available from primary source

- · Here, we are bypassing the register file

- Also called forwarding

#### Observation!

- Technically, this situation is broken

- 1w \$4,0 (\$3) has already read \$3 from regfile

- add \$3,\$2,\$1 hasn't yet written \$3 to regfile

- But fundamentally, everything is OK

- 1w \$4,0(\$3) hasn't actually used \$3 yet

- add \$3,\$2,\$1 has already computed \$3

CIS 501 (Martin): Pipelining 38

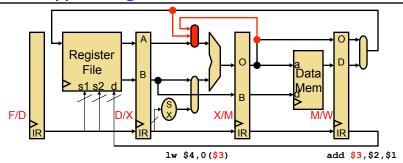

#### **WX** Bypassing

- What about this combination?

- Add another bypass path and MUX (multiplexor) input

- First one was an MX bypass

- This one is a **WX** bypass

CIS 501 (Martin): Pipelining 39 CIS 501 (Martin): Pipelining 40

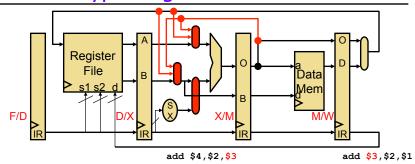

#### **ALUinB Bypassing**

· Can also bypass to ALU input B

CIS 501 (Martin): Pipelining

# **Bypass Logic**

Each MUX has its own, here it is for MUX ALUinA

(D/X.IR.RegSource1 == X/M.IR.RegDest) => 0

(D/X.IR.RegSource1 == M/W.IR.RegDest) => 1

Else => 2

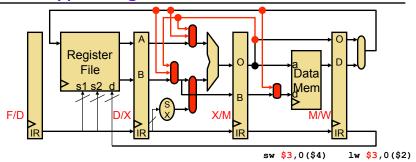

#### WM Bypassing?

- Does WM bypassing make sense?

- Not to the address input (why not?)

- But to the store data input, yes

CIS 501 (Martin): Pipelining 42

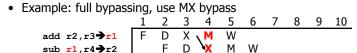

# Pipeline Diagrams with Bypassing

• If bypass exists, "from"/"to" stages execute in same cycle

• Example: full bypassing, use WX bypass

• Example: WM bypass

• Can you think of a code example that uses the WM bypass?

CIS 501 (Martin): Pipelining 43 CIS 501 (Martin): Pipelining 44

41

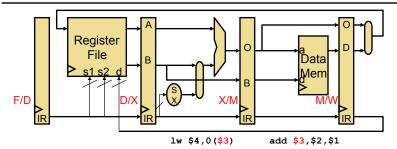

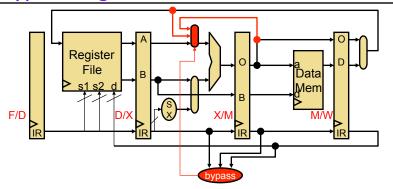

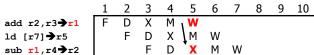

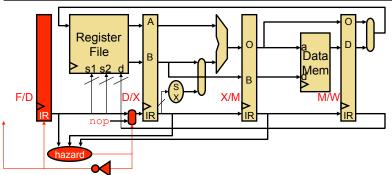

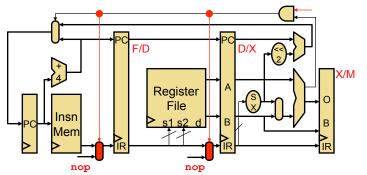

#### Have We Prevented All Data Hazards?

- No. Consider a "load" followed by a dependent "add" insn

- Bypassing alone isn't sufficient!

- Hardware solution: detect this situation and inject a stall cycle

- Software solution: ensure compiler doesn't generate such code CIS 501 (Martin): Pipelining 45

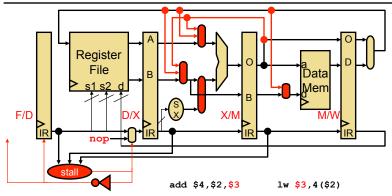

#### Stalling to Avoid Data Hazards

- Prevent F/D insn from reading (advancing) this cycle

- Write nop into D/X.IR (effectively, insert nop in hardware)

- Also reset (clear) the datapath control signals

- Disable F/D latch and PC write enables (why?)

- Re-evaluate situation next cycle

CIS 501 (Martin): Pipelining 46

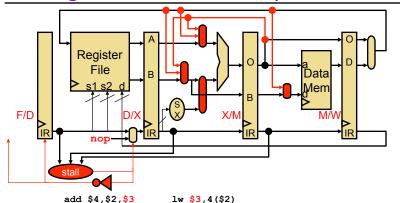

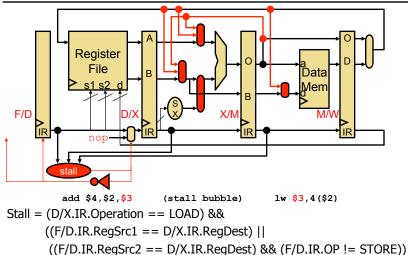

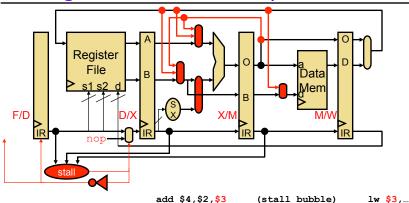

# Stalling on Load-To-Use Dependences

Stall = (D/X.IR.Operation == LOAD) && ((F/D.IR.RegSrc1 == D/X.IR.RegDest) || ((F/D.IR.RegSrc2 == D/X.IR.RegDest) && (F/D.IR.OP != STORE))

# Stalling on Load-To-Use Dependences

CIS 501 (Martin): Pipelining 47 CIS 501 (Martin): Pipelining 48

#### Stalling on Load-To-Use Dependences

add \$4,\$2,\$3 (stall bubble) Stall = (D/X.IR.Operation == LOAD) &&

((F/D.IR.RegSrc1 == D/X.IR.RegDest) ||

((F/D.IR.RegSrc2 == D/X.IR.RegDest) && (F/D.IR.OP != STORE))

CIS 501 (Martin): Pipelining

# Performance Impact of Load/Use Penalty

- Assume

- Branch: 20%, load: 20%, store: 10%, other: 50%

- 50% of loads are followed by dependent instruction

- require 1 cycle stall (I.e., insertion of 1 nop)

- Calculate CPI

- CPI = 1 + (1 \* 20% \* 50%) = 1.1

CIS 501 (Martin): Pipelining 50

# Reducing Load-Use Stall Frequency

|                 | 1 | 2 | 3 | 4  | 5 | 6          | 7 | 8 | 9 |

|-----------------|---|---|---|----|---|------------|---|---|---|

| add \$3,\$2,\$1 | F | D | Х | M  | W |            |   |   |   |

| lw \$4,4(\$3)   |   | F | D | ŧχ | М | w          |   |   |   |

| addi \$6,\$4,1  |   |   | F | d* | D | <b>▼</b> X | М | W |   |

| sub \$8,\$3,\$1 |   |   |   |    | F | D          | Х | М | W |

- Use compiler scheduling to reduce load-use stall frequency

- More on compiler scheduling later

|                 | 1 | 2 | 3 | 4 | 5   | 6          | 7 | 8 | 9 |

|-----------------|---|---|---|---|-----|------------|---|---|---|

| add \$3,\$2,\$1 | F | D | Х | М | W   |            |   |   |   |

| lw \$4,4(\$3)   |   | F | D | X | М   | w          |   |   |   |

| sub \$8 \$3,\$1 |   |   | F | D | * X | М          | W |   |   |

| addi \$6,\$4,1  |   |   |   | F | D   | <b>▼</b> X | М | W |   |

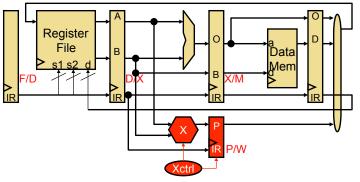

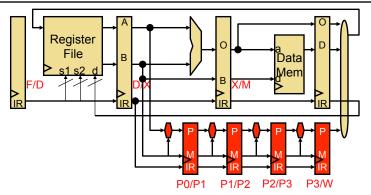

# Pipelining and Multi-Cycle Operations

- What if you wanted to add a multi-cycle operation?

- E.g., 4-cycle multiply

- P/W: separate output latch connects to W stage

- Controlled by pipeline control finite state machine (FSM)

# A Pipelined Multiplier

- Multiplier itself is often pipelined, what does this mean?

- Product/multiplicand register/ALUs/latches replicated

- Can start different multiply operations in consecutive cycles

CIS 501 (Martin): Pipelining 53

# More Multiplier Nasties

- What about...

- Mis-ordered writes to the same register

- Software thinks add gets \$4 from addi, actually gets it from mul

|                  | 1 | 2 | 3  | 4  | 5  | 6  | 7 | 8 | 9 |

|------------------|---|---|----|----|----|----|---|---|---|

| mul \$4,\$3,\$5  | F | D | P0 | P1 | P2 | Р3 | W |   |   |

| addi \$4,\$1,1   |   | F | D  | Х  | М  | w  |   |   |   |

|                  |   |   |    |    |    |    |   |   |   |

|                  |   |   |    |    |    |    |   |   |   |

| add \$10,\$4,\$6 |   |   |    |    | F  | D  | Χ | М | W |

|                  |   |   |    |    |    |    |   |   |   |

- Common? Not for a 4-cycle multiply with 5-stage pipeline

- More common with deeper pipelines

- In any case, must be correct

# Pipeline Diagram with Multiplier

|                               | 1 | 2 | 3  | 4  | 5  | 6  | 7 | 8 | 9 |

|-------------------------------|---|---|----|----|----|----|---|---|---|

| mul \$4,\$3,\$5               | F | D | P0 | P1 | P2 | Р3 | W |   |   |

| addi \$6, <mark>\$4</mark> ,1 |   | F | D  | d* | d* | d* | Х | М | W |

- What about...

- Two instructions trying to write regfile in same cycle?

- Structural hazard!

- Must prevent:

CIS 501 (Martin): Pipelining

|                  | 1 | 2 | 3  | 4  | 5  | 6  | 7 | 8 | 9 |

|------------------|---|---|----|----|----|----|---|---|---|

| mul \$4,\$3,\$5  | F | D | P0 | P1 | P2 | Р3 | W |   |   |

| addi \$6,\$1,1   |   | F | D  | Х  | М  | W  |   |   |   |

| add \$5,\$6,\$10 |   |   | F  | D  | Х  | М  | W |   |   |

54

# Corrected Pipeline Diagram

- With the correct stall logic

- Prevent mis-ordered writes to the same register

- Why two cycles of delay?

|                  | 1 | 2 | 3  | 4  | 5  | 6  | 7 | 8 | 9 |

|------------------|---|---|----|----|----|----|---|---|---|

| mul \$4,\$3,\$5  | F | D | P0 | P1 | P2 | Р3 | W |   |   |

| addi \$4,\$1,1   |   | F | d* | d* | D  | Х  | М | W |   |

|                  |   |   |    |    |    |    |   |   |   |

|                  |   |   |    |    |    |    |   |   |   |

| add \$10,\$4,\$6 |   |   |    |    | F  | D  | Χ | М | W |

|                  |   |   |    |    |    |    |   |   |   |

• Multi-cycle operations complicate pipeline logic

CIS 501 (Martin): Pipelining 55 CIS 501 (Martin): Pipelining 56

#### **Pipelined Functional Units**

- Almost all multi-cycle functional units are pipelined

- Each operation takes N cycles

- But can start initiate a new (independent) operation every cycle

- Requires internal latching and some hardware replication

- + A cheaper way to add bandwidth than multiple non-pipelined units

• One exception: int/FP divide: difficult to pipeline and not worth it

- s\* = structural hazard, two insns need same structure

- · ISAs and pipelines designed to have few of these

- Canonical example: all insns forced to go through M stage

CIS 501 (Martin): Pipelining

#### What About Branches?

- Control hazards options

- Could just stall to wait for branch outcome (two-cycle penalty)

- Fetch past branch insns before branch outcome is known

- Default: assume "not-taken" (at fetch, can't tell it's a branch)

# **Control Dependences and Branch Prediction**

CIS 501 (Martin): Pipelining

58

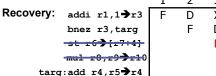

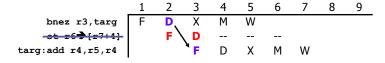

# **Branch Recovery**

- Branch recovery: what to do when branch is actually taken

- Insns that will be written into F/D and D/X are wrong

- Flush them, i.e., replace them with nops

- + They haven't had written permanent state yet (regfile, DMem)

- Two cycle penalty for taken branches

CIS 501 (Martin): Pipelining 59 CIS 501 (Martin): Pipelining 60

#### **Branch Performance**

- Back of the envelope calculation

- Branch: 20%, load: 20%, store: 10%, other: 50%

- Say, 75% of branches are taken

- CPI = 1 + 20% \* 75% \* 2 =1 + 0.20 \* 0.75 \* 2 = 1.3

- Branches cause 30% slowdown

- Even worse with deeper pipelines

- How do we reduce this penalty?

CIS 501 (Martin): Pipelining

61

#### Control Speculation and Recovery

Correct:

bnez r3,targ st r6→[r7+4] mul r8,r9→r10

- Mis-speculation recovery: what to do on wrong guess

- Not too painful in an short, in-order pipeline

- · Branch resolves in X

- + Younger insns (in F, D) haven't changed permanent state

- Flush insns currently in F/D and D/X (i.e., replace with nops)

CIS 501 (Martin): Pipelining

#### Big Idea: Speculative Execution

- Speculation: "risky transactions on chance of profit"

- Speculative execution

- Execute before all parameters known with certainty

- Correct speculation

- + Avoid stall, improve performance

- Incorrect speculation (mis-speculation)

- Must abort/flush/squash incorrect insns

- Must undo incorrect changes (recover pre-speculation state)

- The "game": [%correct \* gain] [(1-%correct) \* penalty]

- **Control speculation**: speculation aimed at control hazards

- Unknown parameter: are these the correct insns to execute next?

62 CIS 501 (Martin): Pipelining

#### Reducing Penalty: Fast Branches

- Fast branch: targets control-hazard penalty

- Basically, branch insns that can resolve at D, not X

- Test must be comparison to zero or equality, no time for ALU

- + New taken branch penalty is 1

- Additional comparison insns (e.g., cmplt, slt) for complex tests

- Must bypass into decode stage now, too

CIS 501 (Martin): Pipelining

#### Fast Branch Performance

- Assume: Branch: 20%, 75% of branches are taken

- CPI = 1 + 20% \* 75% \* 1 = 1 + 0.20\*0.75\*1 = 1.15

- 15% slowdown (better than the 30% from before)

- But wait, fast branches assume only simple comparisons

- · Fine for MIPS

- But not fine for ISAs with "branch if \$1 > \$2" operations

- In such cases, say 25% of branches require an extra insn

- CPI = 1 + (20% \* 75% \* 1) + 20%\*25%\*1(extra insn) = 1.2

- Example of ISA and micro-architecture interaction

- Type of branch instructions

- · What about condition codes?

CIS 501 (Martin): Pipelining

#### **Branch Prediction Performance**

- Parameters

- Branch: 20%, load: 20%, store: 10%, other: 50%

- 75% of branches are taken

- Dynamic branch prediction

- Branches predicted with 95% accuracy

- CPI = 1 + 20% \* 5% \* 2 = 1.02

#### Fewer Mispredictions: Branch Prediction

- Dynamic branch prediction: hardware guesses outcome

- Start fetching from guessed address

- Flush on mis-prediction

CIS 501 (Martin): Pipelining 66

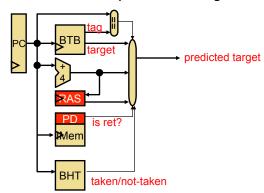

#### **Dynamic Branch Prediction Components**

- Step #1: is it a branch?

- Easy after decode...

- Step #2: is the branch taken or not taken?

- **Direction predictor** (applies to conditional branches only)

- Predicts taken/not-taken

- Step #3: if the branch is taken, where does it go?

- Easy after decode...

65

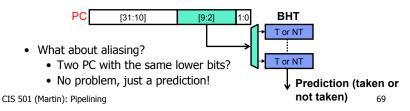

#### **Branch Direction Prediction**

- · Learn from past, predict the future

- Record the past in a hardware structure

- Direction predictor (DIRP)

- Map conditional-branch PC to taken/not-taken (T/N) decision

- Individual conditional branches often biased or weakly biased

- 90%+ one way or the other considered "biased"

- Why? Loop back edges, checking for uncommon conditions

- Branch history table (BHT): simplest predictor

- PC indexes table of bits (0 = N, 1 = T), no tags

- Essentially: branch will go same way it went last time

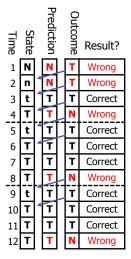

# Two-Bit Saturating Counters (2bc)

- Two-bit saturating counters (2bc) [Smith 1981]

- Replace each single-bit prediction

- (0,1,2,3) = (N,n,t,T)

- Adds "hysteresis"

- Force predictor to mis-predict twice before "changing its mind"

- One mispredict each loop execution (rather than two)

- + Fixes this pathology (which is not contrived, by the way)

- Can we do even better?

#### Branch History Table (BHT)

- Branch history table (BHT): simplest direction predictor

- PC indexes table of bits (0 = N, 1 = T), no tags

- Essentially: branch will go same way it went last time

- Problem: inner loop branch below

for (i=0;i<100;i++)

for (j=0;j<3;j++)

// whatever</pre>

- Two "built-in" mis-predictions per inner loop iteration

- Branch predictor "changes its mind too quickly"

| Time | State | Prediction | Outcome | Result? |

|------|-------|------------|---------|---------|

| 1    | N     | N          | T       | Wrong   |

| 2    | T     | T          | Т       | Correct |

| 3    | T     | Т          | Т       | Correct |

| 4    | T     | T          | N       | Wrong   |

| 5    | N     | N          | T       | Wrong   |

| 6    | Т     | T          | Т       | Correct |

| 7    | T     | Т          | Т       | Correct |

| 8    | T     | T          | N       | Wrong   |

| 9    | N     | N          | T       | Wrong   |

| 10   | T     | T          | Т       | Correct |

| 11   | T     | Т          | Т       | Correct |

| 12   | T     | T          | N       | Wrong   |

CIS 501 (Martin): Pipelining

70

#### **Correlated Predictor**

- Correlated (two-level) predictor [Patt 1991]

- Exploits observation that branch outcomes are correlated

- Maintains separate prediction per (PC, BHR) pairs

- Branch history register (BHR): recent branch outcomes

- Simple working example: assume program has one branch

- BHT: one 1-bit DIRP entry

- BHT+2BHR: 2<sup>2</sup> = 4 1-bit DIRP entries

- Why didn't we do better?

- BHT not long enough to capture pattern

CIS 501 (Martin): Pipelining 72

#### Correlated Predictor – 3 Bit Pattern

Try 3 bits of history

2<sup>3</sup> DIRP entries per pattern

| Time | "Pattern" | NNN | NNT          | NTN | Sta<br>NTT | ттт | Prediction |   | Outcome | Result? |    |   |         |

|------|-----------|-----|--------------|-----|------------|-----|------------|---|---------|---------|----|---|---------|

| 1    | NNN       | N   | N            | N   | N          | N   | N          | N | N       | N       | Γ  | T | Wrong   |

| 2    | NNT       | Т   | N            | N   | N          | N   | N          | N | N       | N       | Γ  | T | Wrong   |

| 3    | NTT       | Т   | Т            | N   | N          | N   | N          | N | N       | N       | Γ  | T | Wrong   |

| 4    | тт        | Т   | Т            | N   | Т          | N   | N          | N | N       | N       | ſ  | N | Correct |

| 5    | TTN       | T   | T            | N   |            | N   | N          | N | N       | N       | [  | T | Wrong   |

| 6    | TNT       | Т   | Т            | N   | Т          | N   | N          | Т | N       | N       | Γ  | T | Wrong   |

| 7    | NTT       | Т   | Т            | N   | Т          | N   | Т          | Т | N       | T       | Γ  | T | Correct |

| 8    | ТТТ       | Т   | Т            | N   | Т          | N   | Т          | Т | N       | N       | Γ  | N | Correct |

| 9    | TTN       | Ť   | Ţ <b>-</b> Ţ | N   |            | N   | Ť          | T | N       | ∏τ∏     | [· | Ŧ | Correct |

| 10   | TNT       | Т   | Т            | N   | Т          | N   | Т          | Т | N       | Т       | Γ  | T | Correct |

| 11   | NTT       | Т   | Т            | N   | T          | N   | Т          | Т | N       | Т       |    | T | Correct |

| 12   | TTT       | Т   | Т            | N   | Т          | N   | Т          | Т | N       | N       |    | N | Correct |

+ No mis-predictions after predictor learns all the relevant patterns! CIS 501 (Martin): Pipelining 7

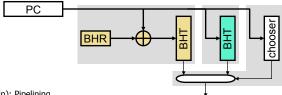

#### **Hybrid Predictor**

- **Hybrid (tournament) predictor** [McFarling 1993]

- Attacks correlated predictor BHT capacity problem

- Idea: combine two predictors

- Simple BHT predicts history independent branches

- Correlated predictor predicts only branches that need history

- Chooser assigns branches to one predictor or the other

- Branches start in simple BHT, move mis-prediction threshold

- + Correlated predictor can be made **smaller**, handles fewer branches

- + 90-95% accuracy

#### Correlated Predictor Design

- Design choice I: one **global** BHR or one per PC (**local**)?

- Each one captures different kinds of patterns

- Global is better, captures local patterns for tight loop branches

- Design choice II: how many history bits (BHR size)?

- Tricky one

- + Given unlimited resources, longer BHRs are better, but...

- BHT utilization decreases

- Many history patterns are never seen

- Many branches are history independent (don't care)

- PC xor BHR allows multiple PCs to dynamically share BHT

- BHR length < log<sub>2</sub>(BHT size)

- Predictor takes longer to train

- Typical length: 8–12

CIS 501 (Martin): Pipelining

74

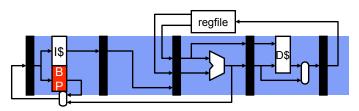

#### When to Perform Branch Prediction?

- Option #1: During Decode

- Look at instruction opcode to determine branch instructions

- Can calculate next PC from instruction (for PC-relative branches)

- One cycle "mis-fetch" penalty even if branch predictor is correct

- Option #2: During Fetch?

- How do we do that?

CIS 501 (Martin): Pipelining  $\downarrow$  75 CIS 501 (Martin): Pipelining 76

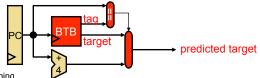

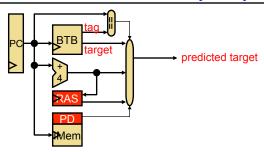

#### Revisiting Branch Prediction Components

- Step #1: is it a branch?

- Easy after decode... during fetch: predictor

- Step #2: is the branch taken or not taken?

- **Direction predictor** (as before)

- Step #3: if the branch is taken, where does it go?

- Branch target predictor (BTB)

- Supplies target PC if branch is taken

CIS 501 (Martin): Pipelining 77

#### **Branch Target Buffer (continued)**

- At Fetch, how does insn know it's a branch & should read BTB? It doesn't have to...

- ...all insns access BTB in parallel with Imem Fetch

- Key idea: use BTB to predict which insn are branches

- Implement by "tagging" each entry with its corresponding PC

- Update BTB on every taken branch insn, record target PC:

- BTB[PC].tag = PC, BTB[PC].target = target of branch

- All insns access at Fetch in parallel with Imem

- Check for tag match, signifies insn at that PC is a branch

- Predicted PC = (BTB[PC].tag == PC) ? BTB[PC].target : PC+4

#### Branch Target Buffer (BTB)

- As before: learn from past, predict the future

- Record the past branch targets in a hardware structure

- Branch target buffer (BTB):

- "guess" the future PC based on past behavior

- "Last time the branch X was taken, it went to address Y"

- "So, in the future, if address X is fetched, fetch address Y next"

- Operation

- A small RAM: address = PC, data = target-PC

- Access at Fetch in parallel with instruction memory

- predicted-target = BTB[hash(PC)]

- Updated at X whenever target != predicted-target

- BTB[hash(PC)] = target

- Hash function is just typically just extracting lower bits (as before)

- Aliasing? No problem, this is only a prediction

CIS 501 (Martin): Pipelining 78

#### Why Does a BTB Work?

- Because most control insns use direct targets

- Target encoded in insn itself → same "taken" target every time

- What about indirect targets?

- ullet Target held in a register ightarrow can be different each time

- · Two indirect call idioms

- + Dynamically linked functions (DLLs): target always the same

- Dynamically dispatched (virtual) functions: hard but uncommon

- Also two indirect unconditional jump idioms

- Switches: hard but uncommon

- Function returns: hard and common but...

CIS 501 (Martin): Pipelining 79 CIS 501 (Martin): Pipelining 80

#### Return Address Stack (RAS)

- Return address stack (RAS)

- Call instruction? RAS[TopOfStack++] = PC+4

- Return instruction? Predicted-target = RAS[--TopOfStack]

- Q: how can you tell if an insn is a call/return before decoding it?

- Accessing RAS on every insn BTB-style doesn't work

- Answer: **pre-decode bits** in Imem, written when first executed

- Can also be used to signify branches

CIS 501 (Martin): Pipelining 81

#### **Branch Prediction Performance**

- Dynamic branch prediction

- 20% of instruction branches

- Simple predictor: branches predicted with 75% accuracy

• CPI =

$$1 + (20\% * 25\% * 2) = 1.1$$

• More advanced predictor: 95% accuracy

- Branch mis-predictions still a big problem though

- Pipelines are long: typical mis-prediction penalty is 10+ cycles

- Pipelines are superscalar (later)

#### **Putting It All Together**

• BTB & branch direction predictor during fetch

• If branch prediction correct, no taken branch penalty

CIS 501 (Martin): Pipelining 82

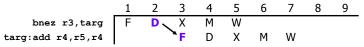

#### Avoiding Branches via ISA: Predication

- Conventional control

- · Conditionally executed insns also conditionally fetched

|                   | 1 | 2 | 3 | 4 | 5 | 6 | 7    | 8      | 9      |      |

|-------------------|---|---|---|---|---|---|------|--------|--------|------|

| beq r3,targ       | F | D | Χ | М | W |   |      |        |        |      |

| sub r6,1,r5       |   | F | D |   |   |   | flus | hed: v | vrong  | path |

| targ:add r4,r5,r4 |   |   | F |   |   |   |      |        | hed: v |      |

| targ:add r4,r5,r4 |   |   |   | F | D | Χ | Μ    | W      |        |      |

- · If beq mis-predicts, both sub and add must be flushed

- Waste: add is independent of mis-prediction

- Predication: not prediction, predication

- ISA support for conditionally-executed unconditionally-fetched insns

- · If beq mis-predicts, annul sub in place, preserve add

- Example is if-then, but if-then-else can be predicated too

- How is this done? How does add get correct value for r5

CIS 501 (Martin): Pipelining 83 CIS 501 (Martin): Pipelining 84

#### **Full Predication**

#### Full predication

- Every insn can be annulled, annulment controlled by...

- Predicate registers: additional register insn (e.g., Itanium)

|                   |                  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9    |      |

|-------------------|------------------|---|---|---|---|---|---|---|---|------|------|

|                   | setp.eq r3,p3    | F | D | Χ | М | W |   |   |   |      |      |

|                   | sub.p r6,1,r5,p3 |   | F | D | Χ |   |   |   |   | annu | lled |

| targ:add r4,r5,r4 |                  |   |   | F | D | Χ | М | W |   |      |      |

Predicate codes: condition bits in each insn (e.g., ARM)

|                   | _              | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9    |      |

|-------------------|----------------|---|---|---|---|---|---|---|---|------|------|

|                   | setcc r3       | F | D | Χ | М | W |   |   |   |      |      |

|                   | sub.nz r6,1,r5 |   | F | D | Χ |   |   |   |   | annu | lled |

| targ:add r4,r5,r4 |                |   |   | F | D | Χ | М | W |   |      |      |

- Only ALU insn shown (sub), but this applies to all insns, even stores

- · Branches replaced with "set-predicate" insns

CIS 501 (Martin): Pipelining 85

#### **Predication Performance**

- Cost/benefit analysis

- Benefit: predication avoids branches

- Thus avoiding mis-predictions

- Also reduces pressure on predictor table (fewer branches to track)

- Cost: extra (annulled) instructions

- As branch predictors are highly accurate...

- Might not help:

- 5-stage pipeline, two instruction on each path of if-then-else

- No performance gain, likely slower if branch predictable

- · Or even hurt!

- But can help:

- Deeper pipelines, hard-to-predict branches, and few added insn

- Thus, prediction is useful, but not a panacea

#### Conditional Register Moves (CMOVs)

#### Conditional (register) moves

Construct appearance of full predication from one primitive

- May require some code duplication to achieve desired effect

- Painful, potentially impossible for some insn sequences

- Requires more registers

- Only good way of retro-fitting predication onto ISA (e.g., x86, Alpha)

CIS 501 (Martin): Pipelining 86

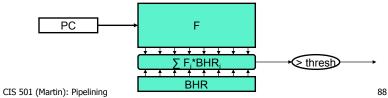

#### Research: Perceptron Predictor

#### • Perceptron predictor [Jimenez]

- Attacks BHR size problem using machine learning approach

- BHT replaced by table of function coefficients F<sub>i</sub> (signed)

- Predict taken if  $\Sigma(BHR_i*F_i)$ > threshold

- + Table size #PC\*|BHR|\*|F| (can use long BHR: ~60 bits)

- Equivalent correlated predictor would be #PC\*2|BHR|

- $\bullet\,$  How does it learn? Update  $F_i$  when branch is taken

- BHR<sub>i</sub> == 1 ?  $F_i$ ++ :  $F_i$ --;

- "don't care" F<sub>i</sub> bits stay near 0, important F<sub>i</sub> bits saturate

- + Hybrid BHT/perceptron accuracy: 95–98%

CIS 501 (Martin): Pipelining 87

#### More Research: GEHL Predictor

- Problem with both correlated predictor and perceptron

- Same BHT real-estate dedicated to 1st history bit (1 column) ...

- ... as to 2nd, 3rd, 10th, 60th...

- Not a good use of space: 1st bit much more important than 60th

- GEometric History-Length predictor [Seznec, ISCA'05]

- Multiple BHTs, indexed by geometrically longer BHRs (0, 4, 16, 32)

- BHTs are (partially) tagged, not separate "chooser"

- Predict: use matching entry from BHT with longest BHR

- Mis-predict: create entry in BHT with longer BHR

- + Only 25% of BHT used for bits 16-32 (not 50%)

- Helps amortize cost of tagging

- + Trains quickly

- 95-97% accurate

Summary

- · Principles of pipelining

- Effects of overhead and hazards

- Pipeline diagrams

- Data hazards

- · Stalling and bypassing

- Control hazards

- Branch prediction

- Predication

CIS 501 (Martin): Pipelining 89 CIS 501 (Martin): Pipelining 90